Are you an artist?

We think so.

Like an artist, you start with a blank canvas. And on that canvas you craft a design that's unique, inspired and, hopefully, the most efficient answer to a problem. That answer, in turn, translates into a product that gives your company a competitive edge in the market.

We call that creative.

At Actel, we understand this process and what you must go through. And we're committed to support your creativity and goals in every way that we can.

First, we support you with proven FPGAs that offer a full range of choices in speed, capacity, pin outs, and packaging. So that you can get the performance you need at a price you can afford.

That's performance/price value from Actel, without painful trade-offs.

Second, we have the advanced design and development tools you need to achieve fast, flexible and predictable design, with guaranteed gate utilization.

Our tools let you capture your vision in silicon, exactly the way you want it.

Third, we provide you with knowledgeable and responsive technical support. Real engineers to answer your questions and help you complete your masterpiece on time, on budget and to your specifications.

You have the ideas and the vision.

We provide the brushes, the paint and the canvas.

# **Fast Flexible Design**

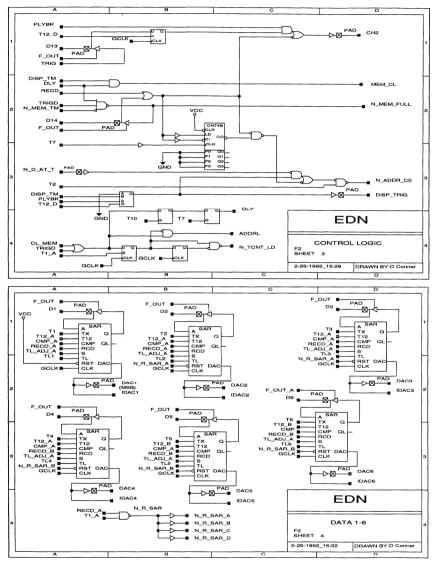

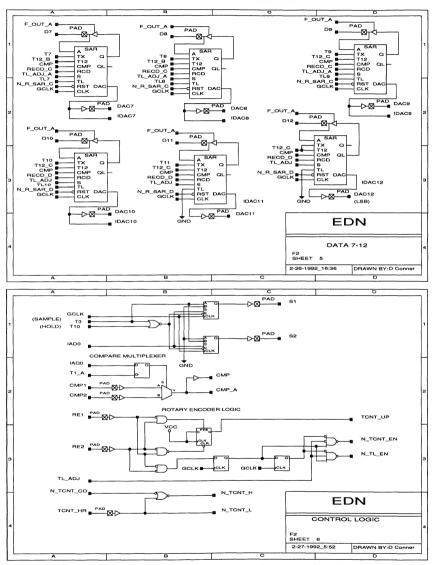

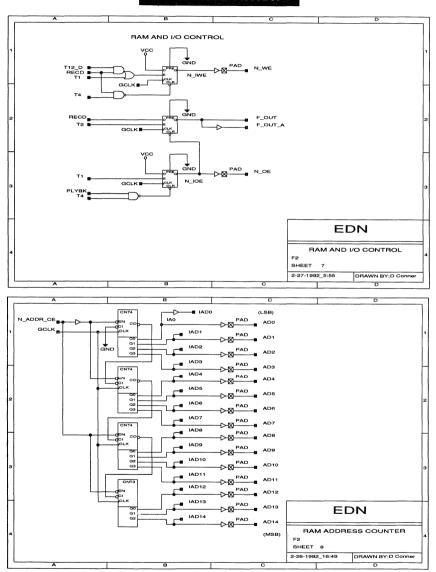

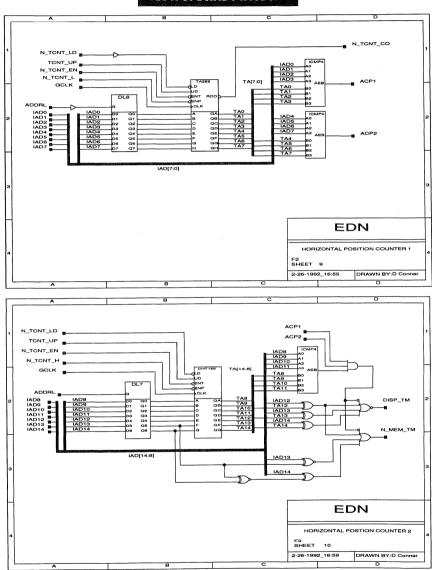

"The Actel design tools are like Hardware Heaven: you draw a schematic, simulate the logic, and view any and all internal nodes... You can place and route the chip in about 30 minutes, then analyze the post-layout timing on the same analyzer. And then, when you are satisfied with the design, you make a chip. All this can be done without ever leaving your PC. This is the way the world should be. Make your boss buy you these tools."

David Erickson Vice President of Hardware Engineering Datacube Corporation

Quote from The Computer Applications Journal, issue #34, May 1993

"Our i860-based numerical accelerator board incorporated four Actel A1460A devices, each implementing one of a wide variety of functions ranging from a DMA controller and four DRAM controllers to control registers and an internal bus controller. The Actel A1460A FPGAs were the only programmable devices available that met the performance, capacity and I/O requirements."

Ken Linton Hardware Engineering Manager SKY Computers

Quote from Actel ACT 3 Press Release, December 13, 1993

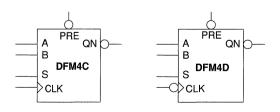

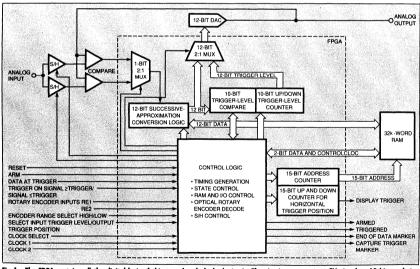

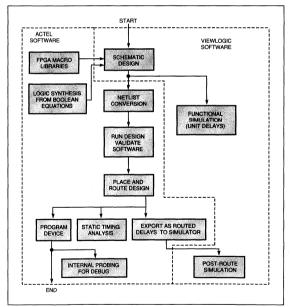

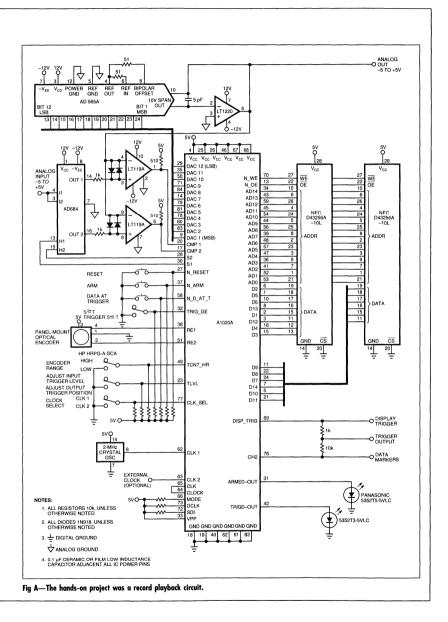

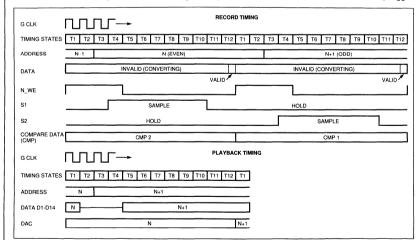

"All things considered, my opinion based on this project is that designing with an FPGA is actually easier than designing with SSI and MSI logic. I no longer wonder what applications FPGAs are useful for, but rather what applications still make sense for small- and medium-scale integration TTL and CMOS logic."

Doug Conner Technical Editor EDN Magazine

Quote from *Hands-on FPGA Project*, parts I and II, *EDN Magazine*, April 9 and 23, 1992. For further details, see complete article reprint in Section 6.

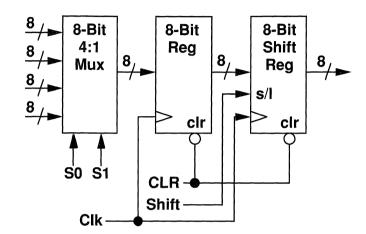

# Integrating PALs and TTL

"It simply wasn't feasible to implement that many shift registers in PALs... The choice was obvious, Actel was the clear winner. Actel's products are easy to work with, offer the highest available logic density and performance and can be relied upon to satisfy the most demanding design requirements."

Mike Casteloes Senior Engineer Interstate Electronics Corporation

For further details, see complete case history in Section 10.

"I was well aware of Actel's technology from the beginning. The Actel devices worked out exceptionally well. I was pleasantly surprised that we were able to integrate as much logic as we could into the parts."

David Kranzler

Engineering Project Leader

3COM Corporation

For further details, see complete case history in Section 10.

# **Computer Systems and Peripherals**

**RasterOps** designed the Actel A1240, a 4,000-gate FPGA, into its PaintBoard Turbo family of graphics products for use with Apple Macintosh computers. The architectural flexibility of the A1240 made it suitable for implementing the varied functions required for the complex Macintosh graphics operations.

# **Telecommunications**

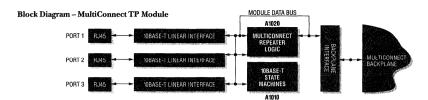

**Chipcom** chose the Actel A1020 FPGA for use in a 24-port twisted pair Ethernet product. Actel believes that its device was selected over competitive SRAM-based FPGAs primarily because of the combination of effective design tools and performance. The Actel circuit architecture also proved more flexible than most PLD architectures in its ability to implement the required logic.

# Military and Aerospace

**Westinghouse** military system engineers replaced 10 standard logic chips with one of Actel's FPGAs, which handled the entire error correction, registration and interface logic for Westinghouse's high speed, high dynamic range analog-to-digital converters.

# **Industrial Control Equipment**

**Siemens Medical Electronics** cut its production cycle by an estimated two months by using Actel's FPGAs for both prototype development and production for a pulse oximetry system. Siemens' engineers produced a working prototype only two weeks after delivery of Actel's development system. All of the microprocessor interface logic was implemented on one of Actel's FPGAs.

# Actel FPGA Data Book and Design Guide

1994

Contributors: Tara Anderson, Sam Beal, Larry Blessman, Sanjiv Desai, Tracy Fang, Gervais Fong, Steve Gurklys, Ken Hayes, Yousef Khalilollahi, Kamal Koraitem, Warren Miller, Kirk Owyang, Hitesh Patel, Quat Tran, and Bruce Weyer.

Special thanks to many other contributors throughout Actel without whom this document could not have been completed.

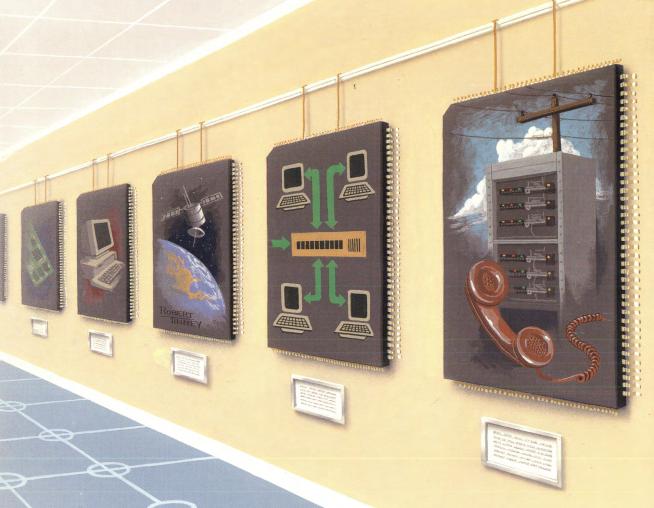

Cover art was designed by Robert F. Tinney of Robert Tinney Graphics.

ACT, ACTmap, and Designer Advantage are trademarks of Actel Corporation. The Actel logo, Action Logic, Activator, Actionprobe, and PLICE are registered trademarks.

This document includes trademarks and registered trademarks of companies other than Actel Corporation, including: 386, 486, ABEL, ACT'x'press, Cadence, Composer, Concept, HP700, Logic Workbench, Mentor Graphics, NETED, OrCAD, PAL, Powerview, PREP, PROcapture, Quicksim II, RapidSIM, Silicon Signature, Sun, Sun Workstation, Verilog, ViewDraw, Viewlogic, ViewSim, Windows, and X Window.

Actel Corporation reserves the right to make changes to any products or services herein at any time without notice. Actel does not assume any responsibility or liability arising out of the application or use of any product or service described as expressly agreed to in writing by Actel.

© 1993 Actel Corporation

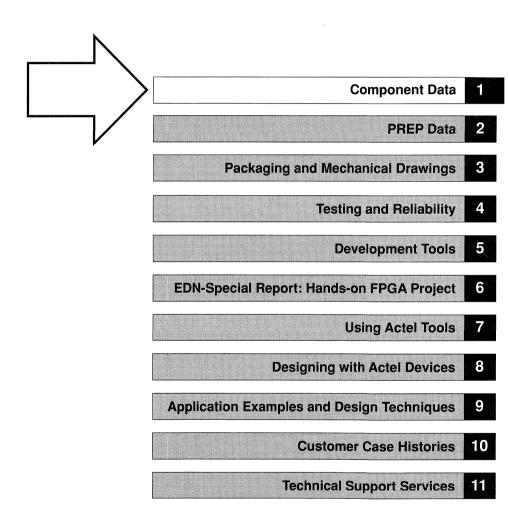

# Actel FPGA Data Book and Design Guide

Order of Contents

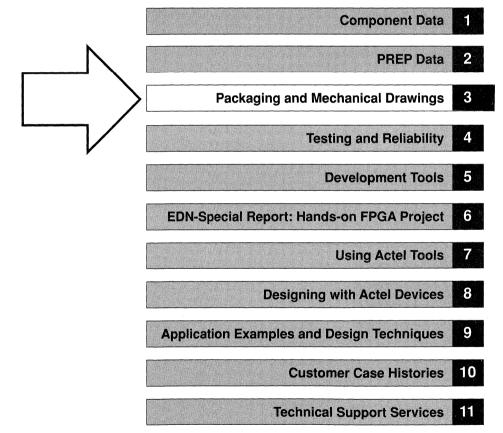

|            | Introduction                                                                    | vi    |

|------------|---------------------------------------------------------------------------------|-------|

| Section 1: | Component Data                                                                  |       |

|            | Product Selector Guide                                                          | 1-1   |

|            | ACT 1 Field Programmable Gate Arrays                                            | 1-3   |

|            | ACT 2 Field Programmable Gate Arrays                                            | 1-31  |

|            | ACT 3 Field Programmable Gate Arrays                                            | 1-79  |

|            | ACT 1 and ACT 2 Military Field Programmable Gate Arrays                         | 1-139 |

| Section 2: | PREP Data                                                                       |       |

|            | Introduction to PREP <sup>™</sup> Benchmarks                                    | 2-1   |

|            | PREP <sup>™</sup> Benchmarks Confirm Cost-Effectiveness of FPGAs                | 2-3   |

|            | Actel PREP <sup>™</sup> Benchmark Results                                       | 2-7   |

|            | Estimating FPGA Applications Performance Using PREP <sup>™</sup> Benchmarks     | 2-17  |

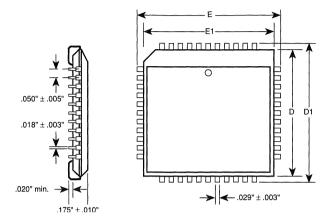

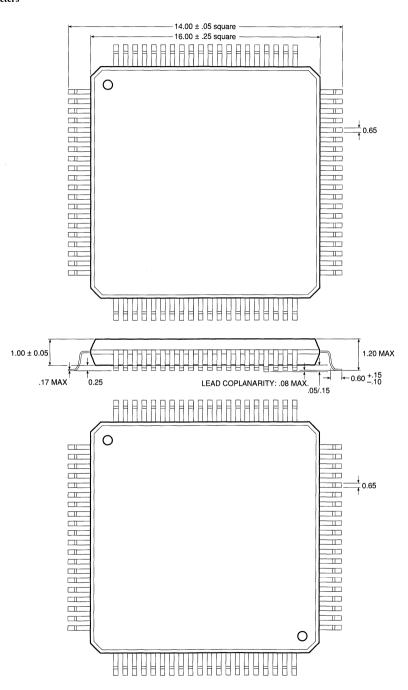

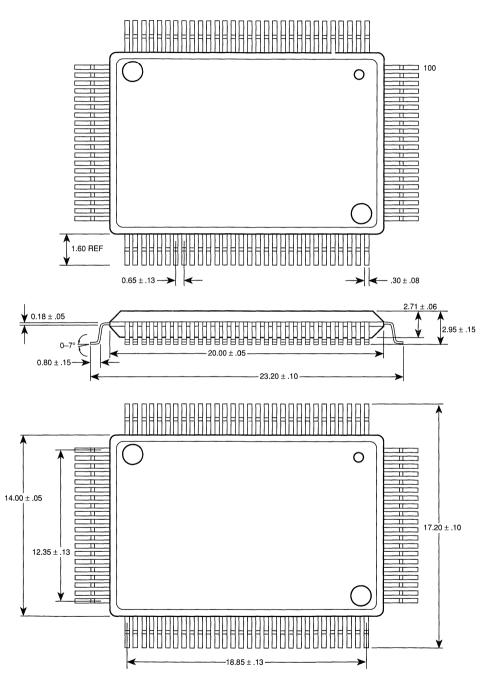

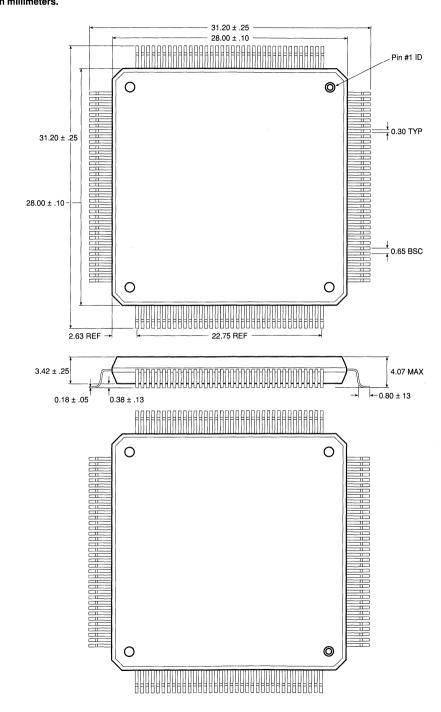

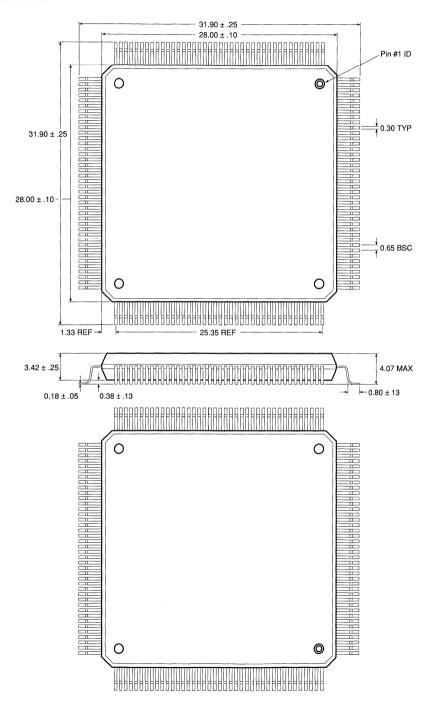

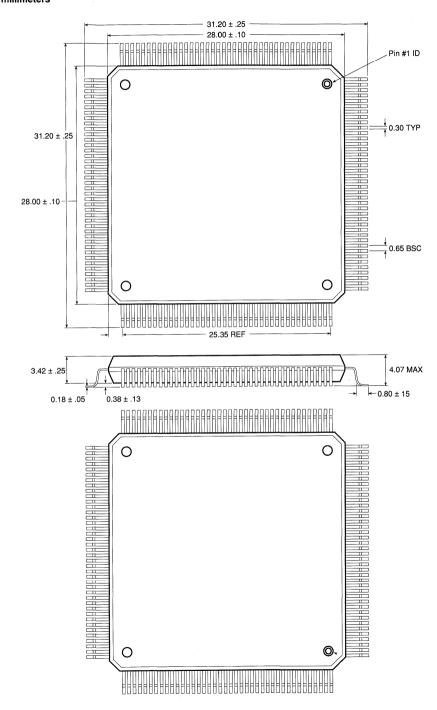

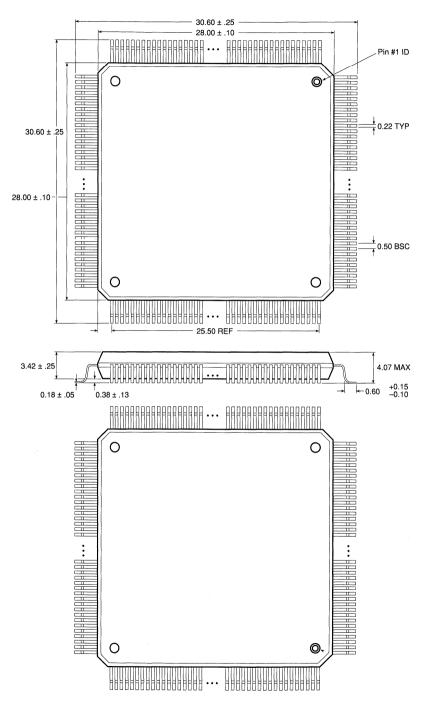

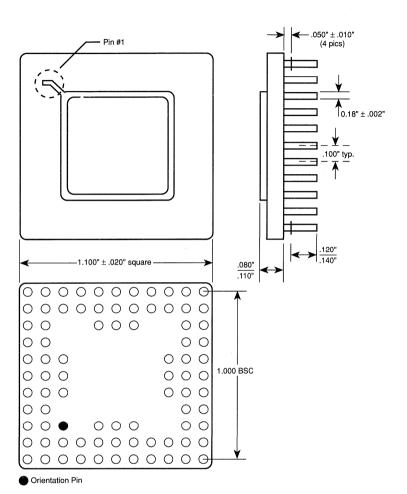

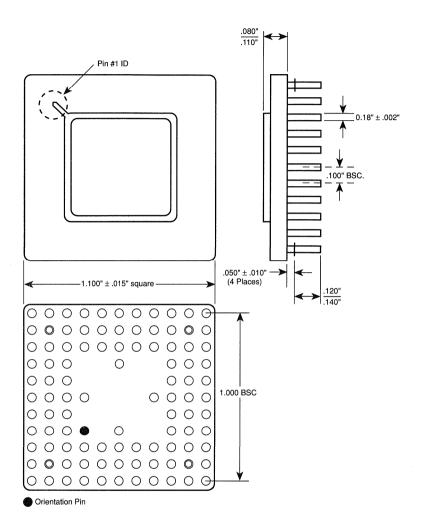

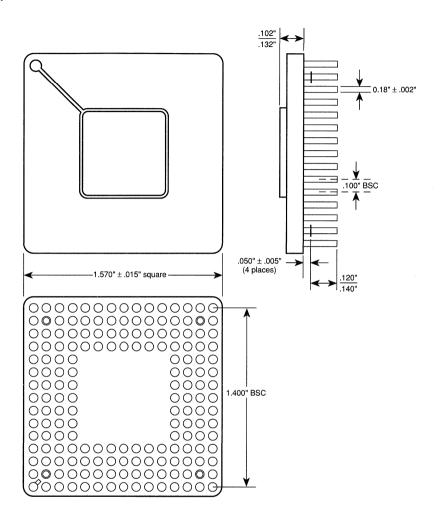

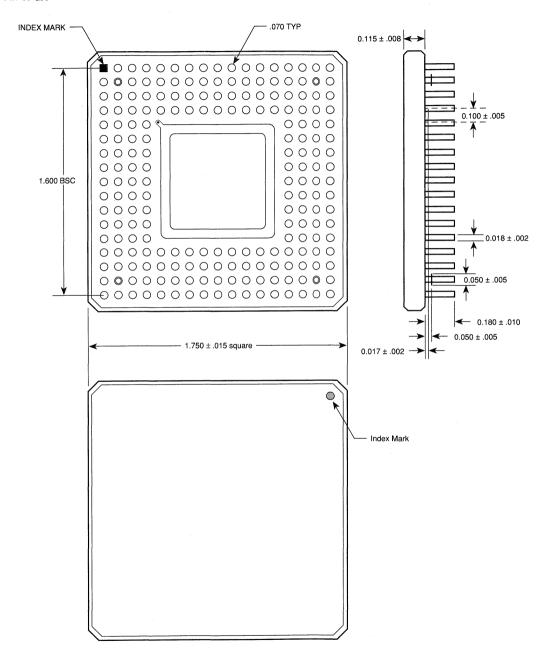

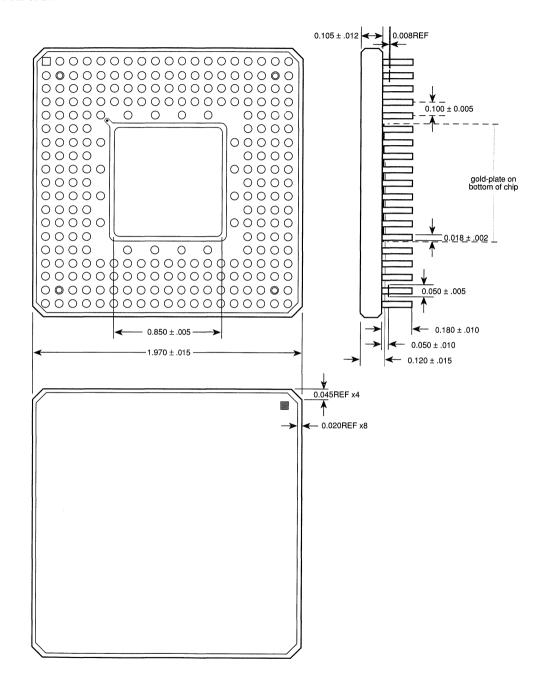

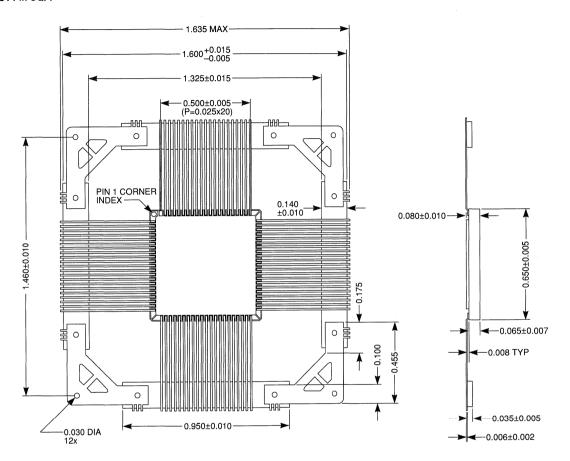

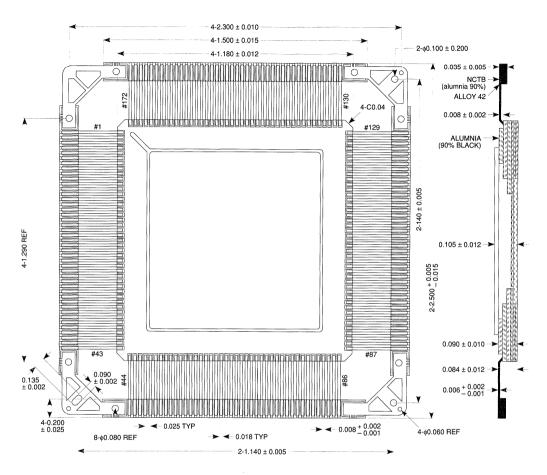

| Section 3: | Packaging and Mechanical Drawings                                               |       |

|            | Package Options: User I/Os per Package                                          | 3-1   |

|            | Package Thermal Characteristics                                                 | 3-3   |

|            | Package Mechanical Drawings                                                     | 3-5   |

|            | Socket Recommendation for Actel FPGA Packages                                   | 3-23  |

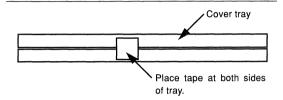

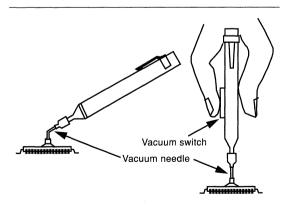

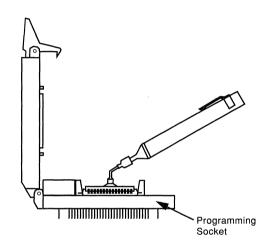

|            | PQFP Handling Instructions                                                      | 3-25  |

| Section 4: | Testing and Reliability                                                         |       |

|            | Testing and Programming Actel Field Programmable Gate Arrays (FPGAs)            | 4-1   |

|            | ACT Family Reliability Report                                                   | 4-9   |

|            | Antifuse Field Programmable Gate Arrays                                         | 4-29  |

|            | Oxide-Nitride-Oxide Antifuse Reliability                                        | 4-45  |

|            | Conductive Channel in ONO Formed by Controlled Dielectric Breakdown             | 4-53  |

|            | Metastability of ACT 1 Devices                                                  | 4-55  |

| Section 5: | Development Tools                                                               |       |

|            | System Product Selector Guide                                                   | 5-1   |

|            | Designer and Designer Advantage System Environment                              | 5-3   |

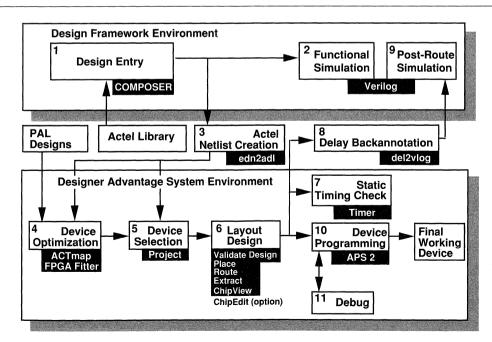

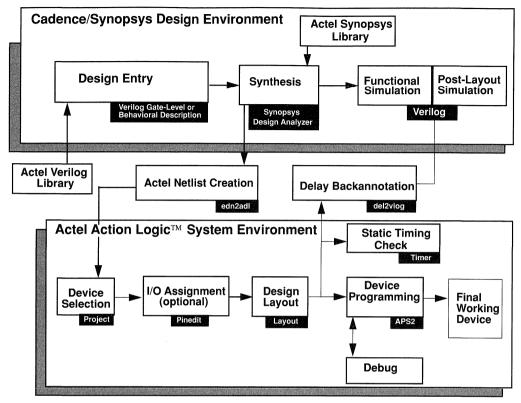

|            | Designer and Designer Advantage System with Cadence Composer/Verilog Design Kit | 5-7   |

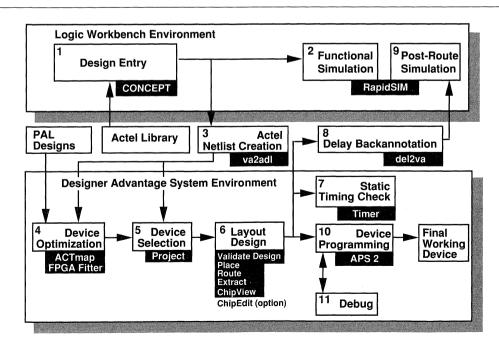

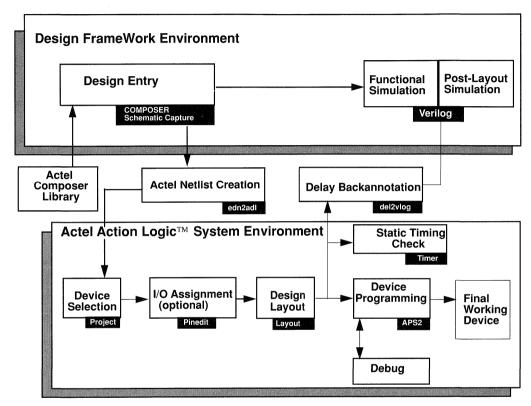

|            | Designer and Designer Advantage System with Cadence Concept/RapidSIM Design Kit | 5-9   |

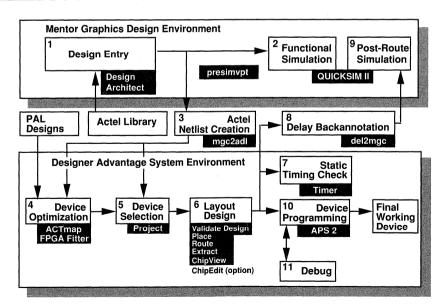

|            | Designer Advantage System with Mentor Graphics Design Kit                       | 5-11  |

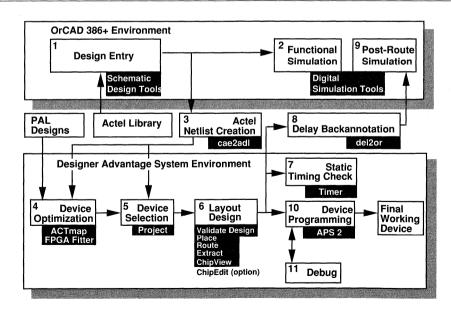

|            | Designer and Designer Advantage System with OrCAD Design Kit                    | 5-15  |

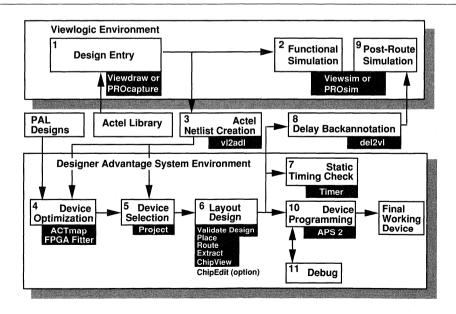

|            | Designer and Designer Advantage System with Viewlogic Design Kit                | 5-17  |

|            | Logic Synthesis Libraries                                                       | 5-21  |

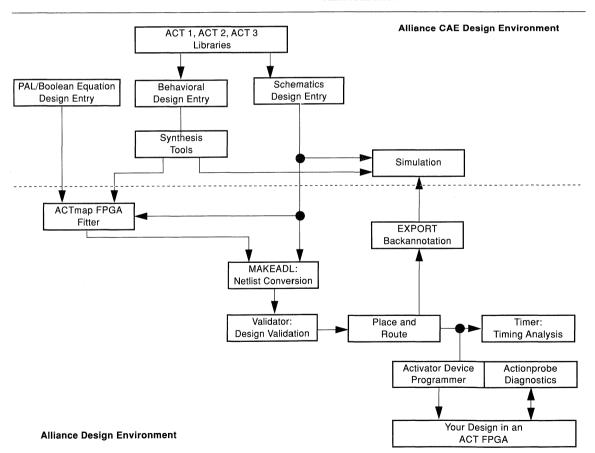

|            | Actel's Industry Alliance Program                                               | 5-23  |

|            | Activator® 2 and Activator 2S Programmers                                       | 5-25  |

© 1993 Actel Corporation

|            | ACT 1 Hard Macro Library Overview                                      | 5-27<br>5-41 |

|------------|------------------------------------------------------------------------|--------------|

|            | ·                                                                      | 5-41         |

| Section 6: | EDN-Special Report: Hands-on FPGA Project                              |              |

|            | Taking the First Steps                                                 | 6-1          |

|            | Migrating to FPGAs: Any Designer Can Do It                             | 6-17         |

| Section 7: | Using Actel Tools                                                      |              |

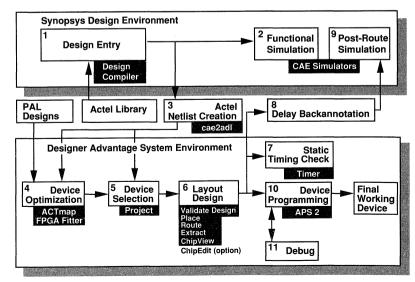

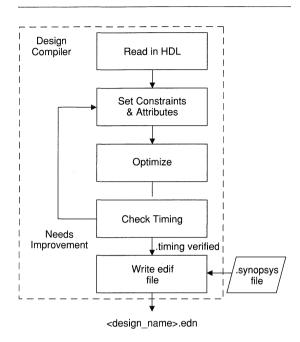

|            | High-Level FPGA Design in the Synopsys Environment                     | 7-1          |

|            | Actel's Cadence Interface                                              | 7-3          |

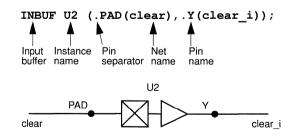

|            | Instantiating Actel's I/O Buffers in Verilog HDL                       | 7-7          |

|            | ALS EDIF Reader and Writer                                             | 7-9          |

|            | Mentor Graphics V7 toV8.2 Design Conversion                            | 7-11         |

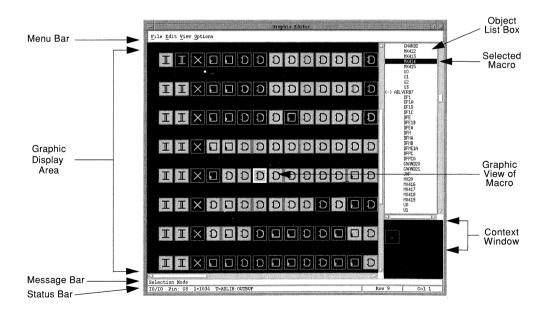

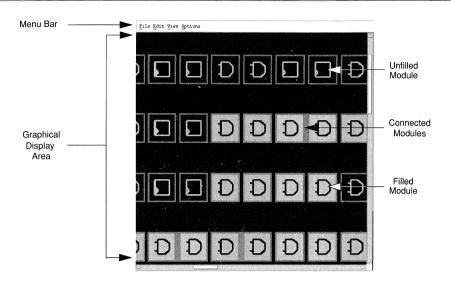

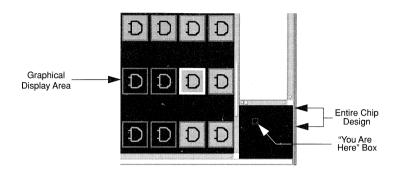

|            | Actel ChipEdit                                                         | 7-13         |

|            | ACTmap <sup>™</sup> Design Flow                                        | 7-17         |

|            | Selecting and Modifying I/O Assignments                                | 7-21         |

|            | Critical Path Analysis Using the Timer                                 | 7-25         |

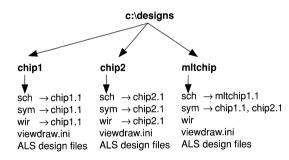

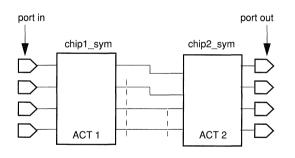

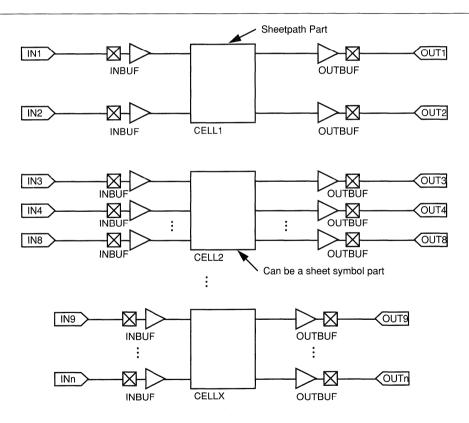

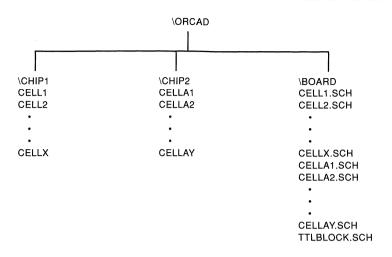

|            | Multichip Post-Layout Simulation Using ALS and Viewsim                 | 7-31         |

|            | Board Level Post-Layout Simulation Using ALS and QuickSim II           | 7-33         |

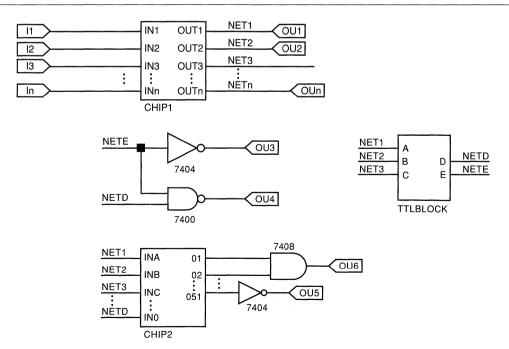

|            | Board-Level Simulation Using ALS/OrCAD                                 | 7-35         |

|            | External Probe Pin Control for Actel FPGAs                             | 7-39         |

|            | Using Actionprobe® Diagnostic Tools                                    | 7-43         |

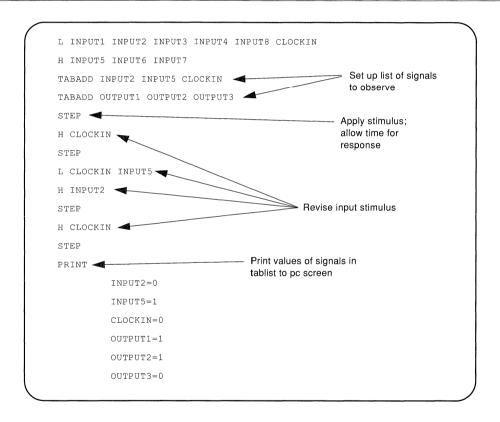

|            | Using the Actel Debugger as a Functional Tester                        | 7-45         |

|            | Moving Actel FPGA Designs from Prototype to Production                 | 7-49         |

|            | Production Programming for Actel FPGAs                                 | 7-51         |

| Section 8: | Designing with Actel Devices                                           |              |

|            | Introduction to FPGA System Design                                     | 8-1          |

|            | An FPGA Family Optimized for High Densities and Reduced Routing Delays | 8-5          |

|            | Estimating Actel FPGA Device Capacity                                  | 8-9          |

|            | Estimating Capacity and Performance for ACT 2 FPGA Designs             | 8-11         |

|            | The Hidden Cost of Reprogrammability                                   | 8-25         |

|            | Actel Logic Modules                                                    | 8-27         |

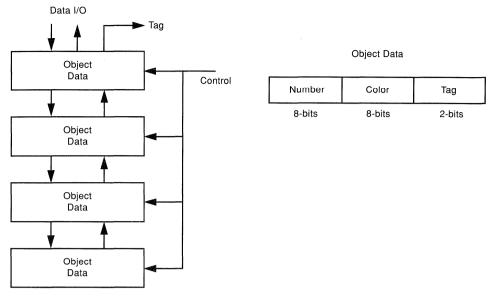

|            | Binning Circuit of Actel FPGAs                                         | 8-31         |

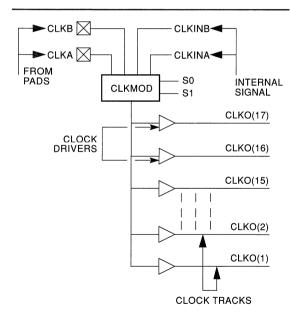

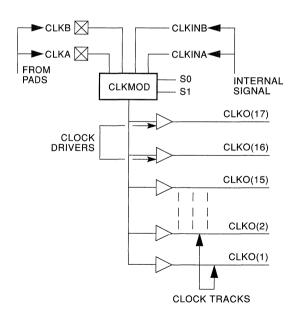

|            | Global Clock Networks                                                  | 8-35         |

|            | Using Dedicated Clock and Clear for ACT 3 Registered I/O Macros        | 8-39         |

|            | Designing for Combinability with the ACT 2 and ACT 3 Architectures     | 8-41         |

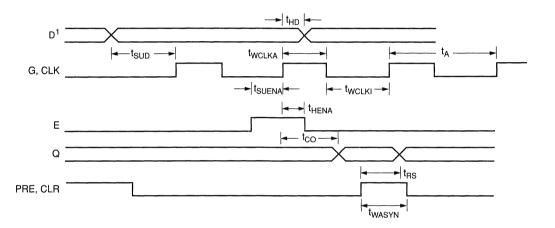

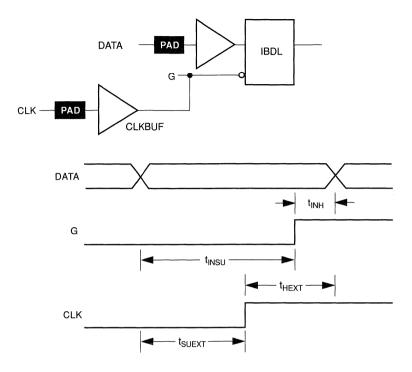

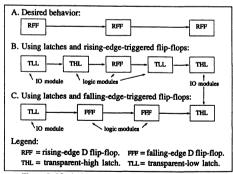

|            | Fast On and Off Chip Delays with ACT 2 I/O Latches                     | 8-45         |

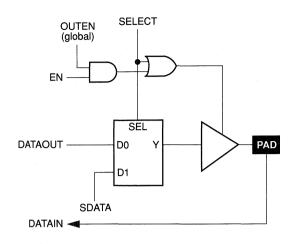

|            | Three-Stating ACT Device I/O Pins for Board Level Testing              | 8-49         |

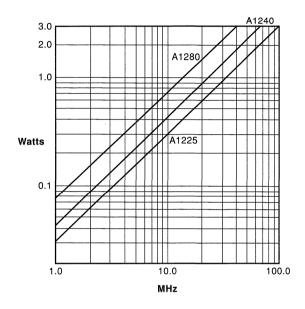

|            | Predicting the Power Dissipation of Actel FPGAs                        | 8-51         |

|            | Board Level Considerations for Actel FPGAs                             | 8-57         |

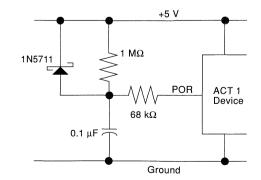

|            | A Power-On Reset (POR) Circuit for Actel Devices                       | 8-65         |

|            | Simultaneously Switching Output Limits for Actel FPGAs                 | 8-67         |

|            |                                                                        |              |

| Section 9:  | Application Examples and Design Techniques                                        |       |

|-------------|-----------------------------------------------------------------------------------|-------|

|             | Hints and Tips for Better Actel Designs I                                         | 9-1   |

|             | Hints and Tips for Better Actel Designs II                                        | 9-3   |

|             | A TTL Designer's Guide to FPGA Design                                             | 9-5   |

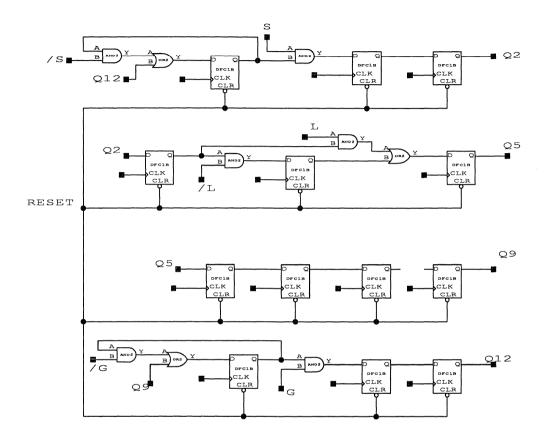

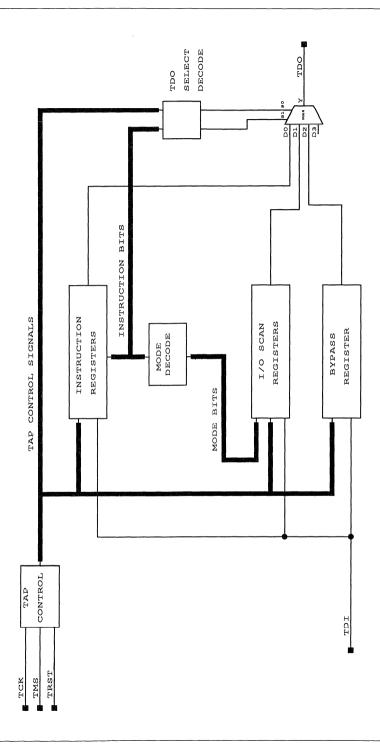

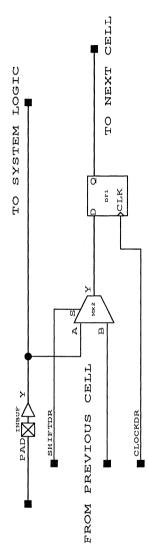

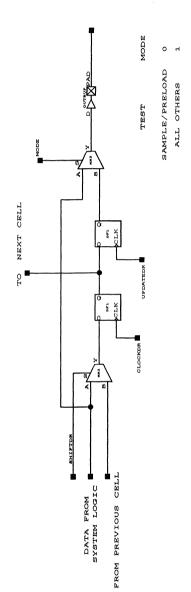

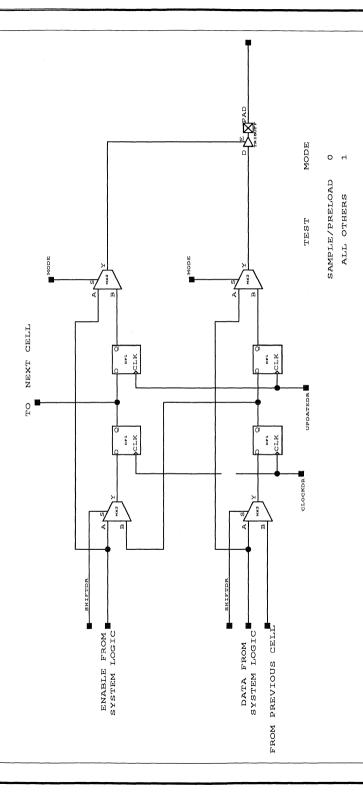

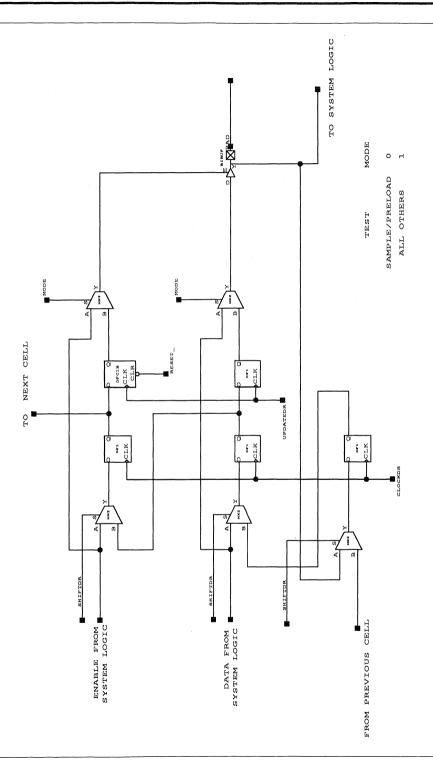

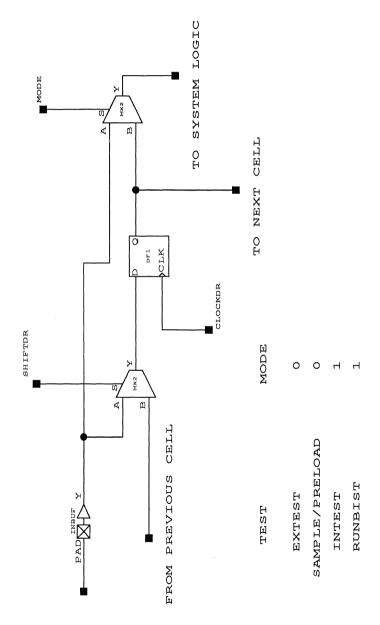

|             | JTAG Implementation in ACT 2 Devices                                              | 9-11  |

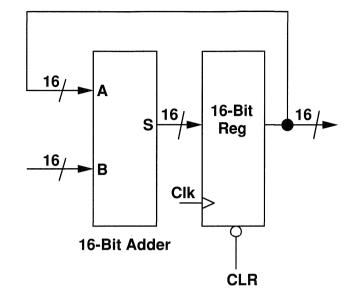

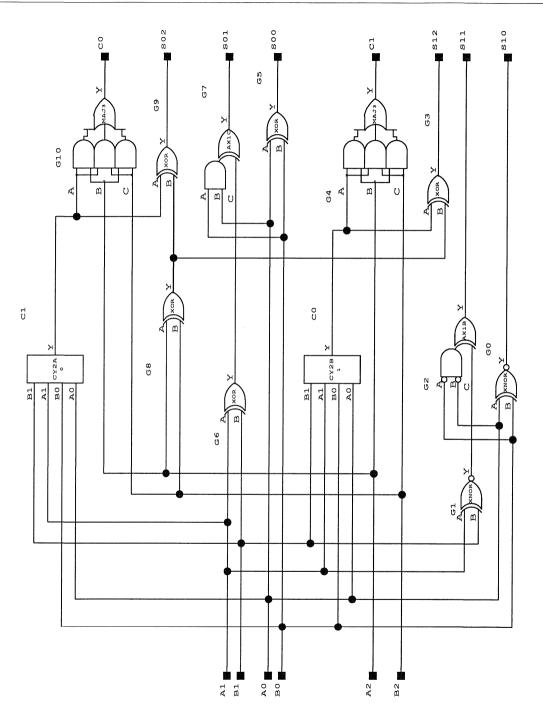

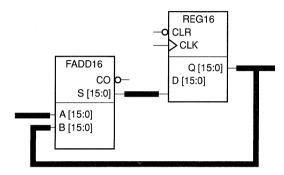

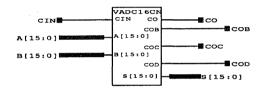

|             | Designing Adders and Accumulators with the ACT 2 Architecture                     | 9-29  |

|             | Fast Adder Design Techniques                                                      | 9-35  |

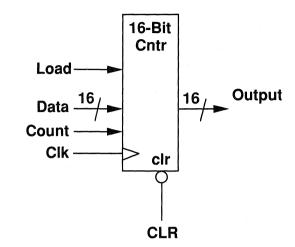

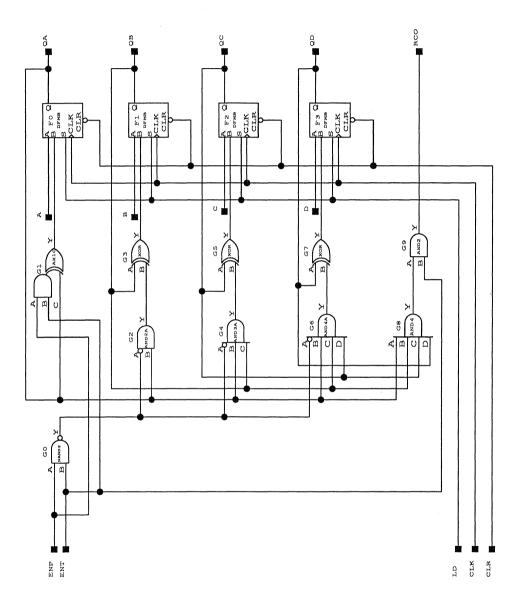

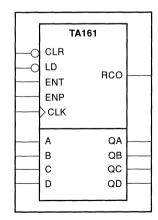

|             | Designing Counters with the ACT 2 Architecture                                    | 9-37  |

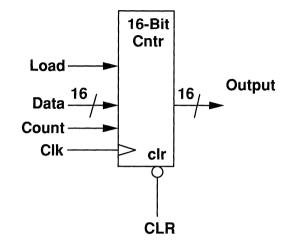

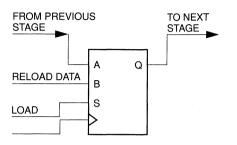

|             | Implementing Load Latency Fast Counters with ACT 2 FPGAs                          | 9-43  |

|             | Bit-Per-State Decoded State Machine for FPGAs                                     | 9-51  |

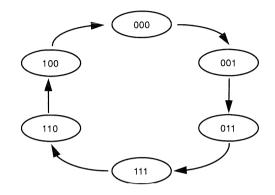

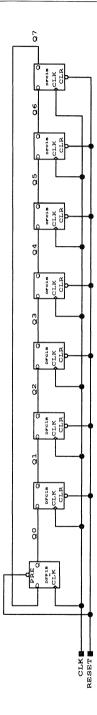

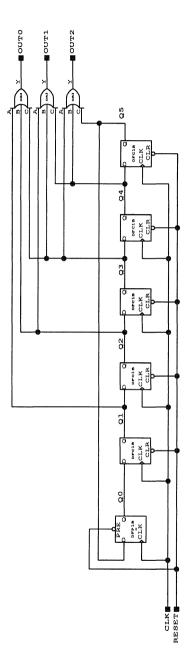

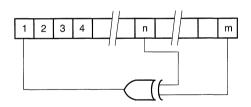

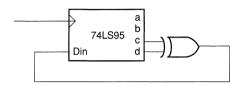

|             | Implementing State Machines Using Shift Registers                                 | 9-55  |

|             | Designing with Pseudo-Random Number Generators                                    | 9-59  |

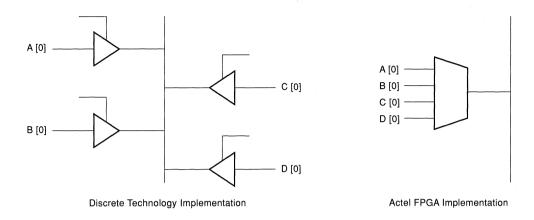

|             | Implementing Three-State and Bidirectional Buses with Multiplexers in Actel FPGAs | 9-61  |

|             | Oscillators for Actel FPGAs                                                       | 9-65  |

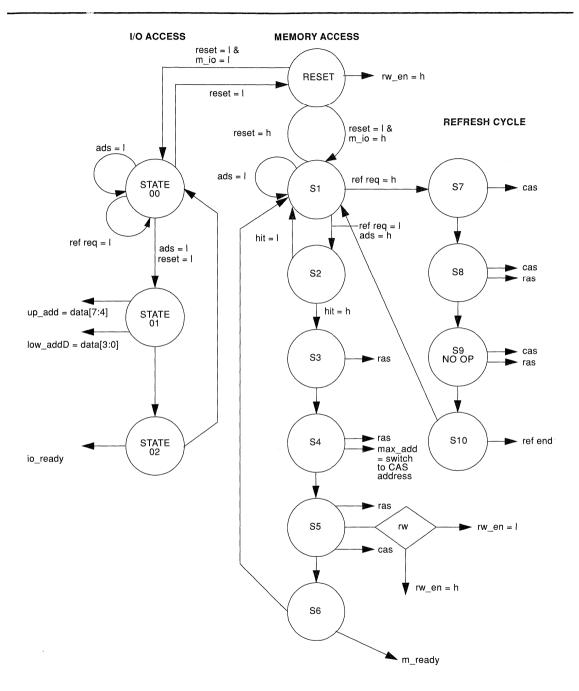

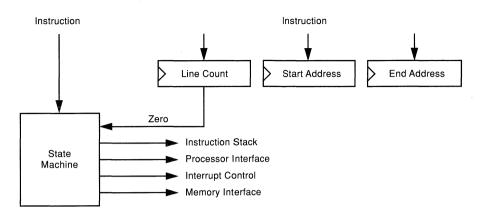

|             | Page Mode DRAM Controller                                                         | 9-67  |

|             | Designing a DRAM Controller Using Language-Based Synthesis                        | 9-69  |

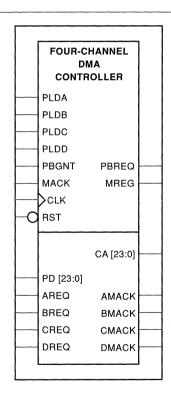

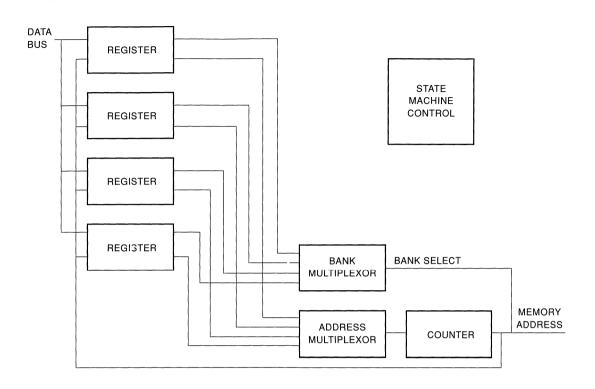

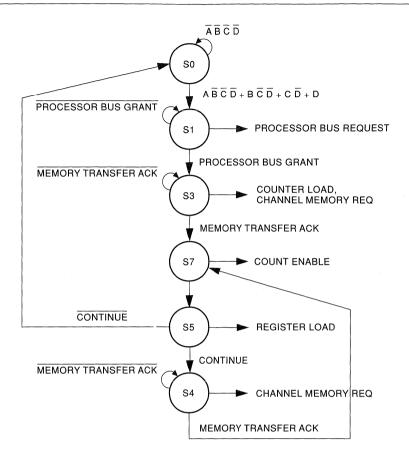

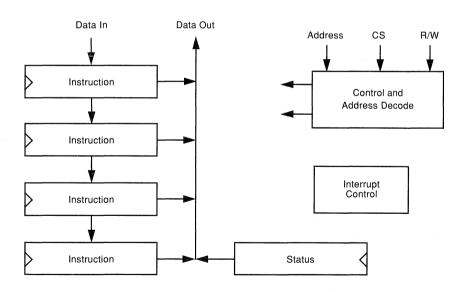

|             | Four-Channel DMA Controller                                                       | 9-81  |

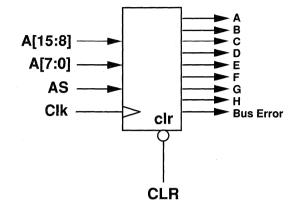

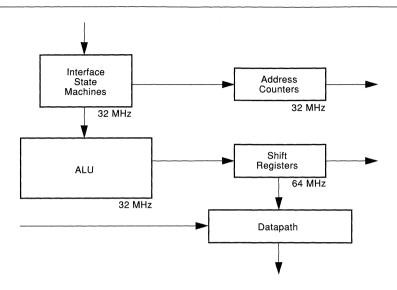

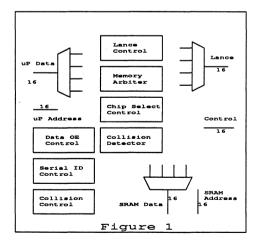

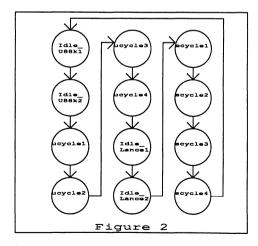

|             | A High-Performance Networking Interface Using Actel FPGAs                         | 9-85  |

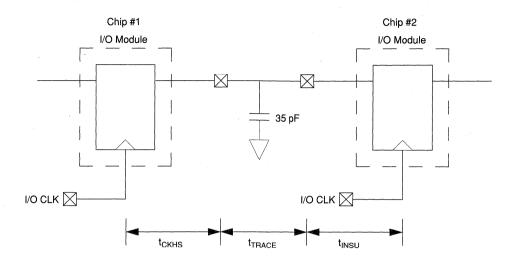

|             | A High-Performance Synchronous Memory Interface Using Actel FPGAs                 | 9-91  |

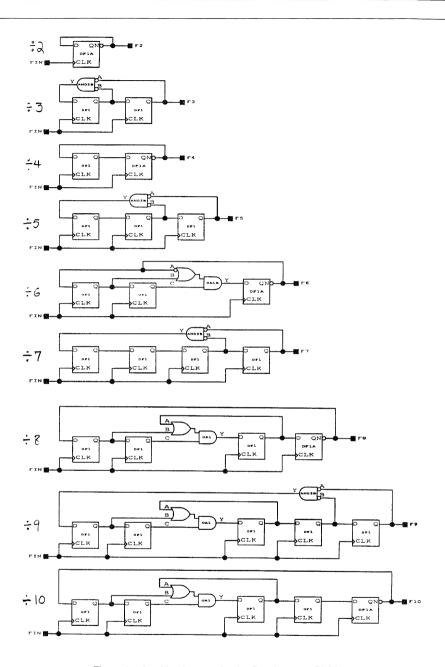

|             | Synchronous Dividers in Actel FPGAs                                               | 9-97  |

|             | A Stepper Motor Controller in an Actel FPGA                                       | 9-101 |

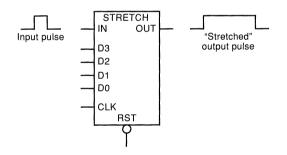

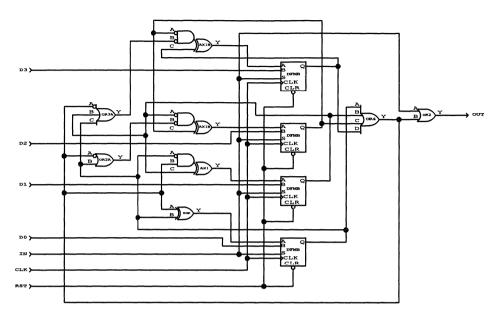

|             | A Pulse Stretching Circuit for Actel FPGAs                                        | 9-105 |

|             | Using FPGAs for Digital PLL Applications                                          | 9-107 |

| Section 10: | Customer Case Histories                                                           |       |

|             | 3COM Corporation — Lan Controller                                                 | 10-1  |

|             | Beckworth Enterprises, Inc. — SBUS-to-Printer Channel Controller                  | 10-3  |

|             | Interstate Electronics — Parallel Processing Demodulation                         | 10-5  |

|             | Delphi Systems — DSP Speech Compression                                           | 10-7  |

|             | GE Medical Systems — Medical Imaging                                              | 10-9  |

|             | Chipcom Co. — State Machine                                                       | 10-13 |

| Section 11: | Technical Support Services                                                        |       |

|             | Technical Support Services                                                        | 11-1  |

# Introduction

#### **Actel Company Background**

Actel Corporation is a leading supplier of high performance field programmable gate arrays (FPGAs) and currently provides the dominant antifuse-based architecture in the FPGA market. As a Sunnyvale-based start-up in 1988, Actel Corporation was the first company to successfully develop and manufacture an antifuse-based FPGA, enabling its products to surpass the performance, density, and cost-per-gate of existing memory-based FPGAs. Actel's lead continues to escalate, and today Actel's advanced product lines are endorsed by electronics industry leaders it has partnered with. Actel's partners include Hewlett-Packard Company, Texas Instruments, and Matsushita Electronics Corporation (Panasonic).

#### The FPGA Market

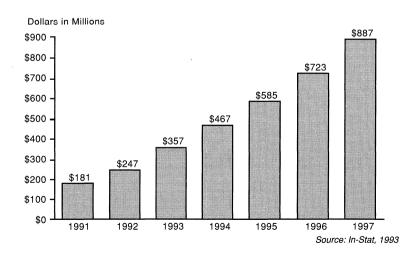

In the past five years, the FPGA market has experienced tremendous growth and currently is the fastest growing segment of the \$5.7 billion ASIC market. Researchers, such as In-Stat Inc., predict that the FPGA market will reach \$887 million by 1997, representing a compound annual growth rate of 30 percent (see Figure 1).

#### Why is the FPGA market growing so fast?

Because a top priority for every engineer today is how to shorten the design cycle, FPGAs have become an important factor in new product development. Offering the design flexibility and capacity of gate arrays, plus the convenience and speed of desktop programming, FPGAs deliver a quicker time-to-market solution than any other method of logic integration.

At the same time, engineers are still facing the traditional demands to make new products cheaper and smaller. FPGAs provide an important solution to this problem, too. By integrating thousands of gates of random logic onto one chip, designers can reduce board space, component count, and power requirements at the same time.

#### **FPGAs versus Conventional Logic**

While discrete logic and programmable logic devices (PLDs) have long been a viable solution for high speed and high drive capability, conventional logic has relinquished part of the market to more integrated solutions such as FPGAs. Compared to conventional logic, FPGAs can:

- · reduce system size (fewer devices)

- · reduce system costs

- · improve system performance

- · improve system reliability (fewer devices on the board)

#### **FPGAs versus Masked Gate Arrays**

FPGAs also offer clear advantages over masked gate arrays, which are traditionally considered the high end of the logic

Figure 1. The FPGA Market

© 1993 Actel Corporation

market. Since 1991, the category that includes FPGAs has realized more annual designs than masked gate arrays, according to Dataquest. Compared to masked gate arrays, FPGAs offer:

- · reduced time-to-market

- increased flexibility

- lower cost for small and medium-size volumes

- low-risk design options (no NRE costs)

#### **Actel FPGA Families**

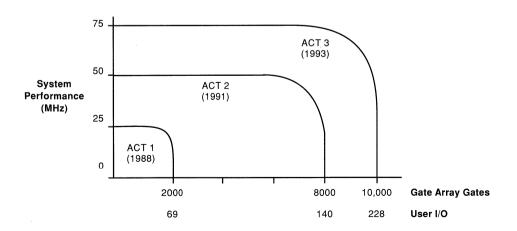

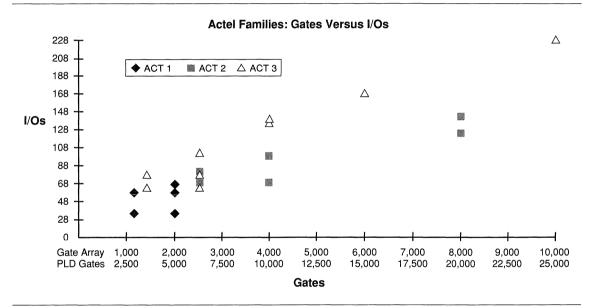

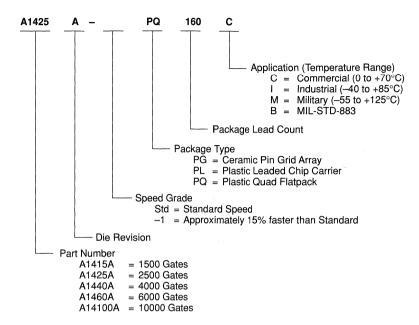

Actel currently offers the ACT™ 1, ACT 2, and ACT 3 families of FPGAs that span 1,200 to 10,000 gates in density (see Figure 2). These families of devices are based on proprietary architecture and interconnect technologies and offer users reliable, risk-free logic integration. The company's strong emphasis on architecture, routing, and programming technologies has enabled Actel to emerge as the technology leader in the FPGA market. The foundation of Actel's technology is the unique synergy created by the company's novel programming element, the PLICE® (Programmable Low-Impedance Circuit Element) antifuse and Actel's multiple-patented FPGA architecture. The advanced performance, capacity, low cost, and ease-of-use characteristics of the ACT families are highly dependent on this synergy. Indeed, Actel's antifuse and architecture must be used together to attain the benefits that Actel devices offer.

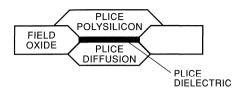

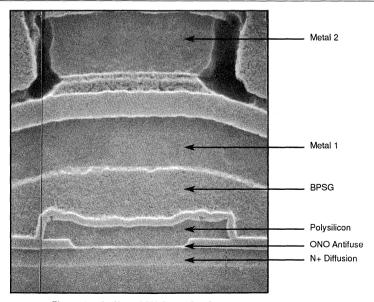

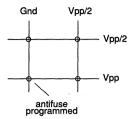

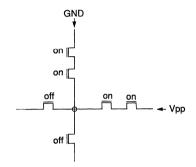

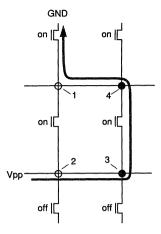

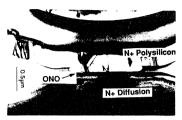

#### Actel's Patented PLICE Antifuse

The PLICE antifuse is a nonvolatile, two-terminal element that exhibits low "on" resistance when programmed and provides the same wire-to-wire interconnect functions as "vias" provide in mask-programmable gate arrays and that transistor-based EPROM and RAM cells and metal fuses provide in conventional programmable logic devices.

Figure 3. The PLICE Antifuse Element

The PLICE antifuse offers key advantages in both size and electrical properties (see Figure 3). The antifuse is small enough that it fits within the width of the channeled routing track. This means that there is basically no die size overhead created by the antifuse itself. The combination of small size and low delay characteristics of the PLICE antifuse has allowed Actel to make two key architectural breakthroughs:

- to offer abundant routing resources while offering very small die sizes

- to offer a highly flexible, highly granular architecture (small logic blocks)

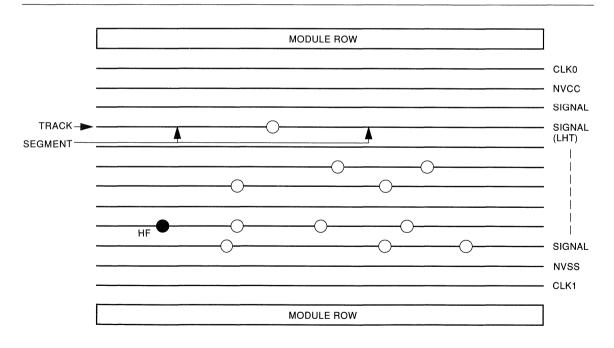

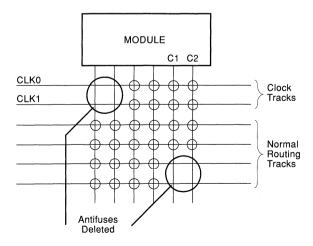

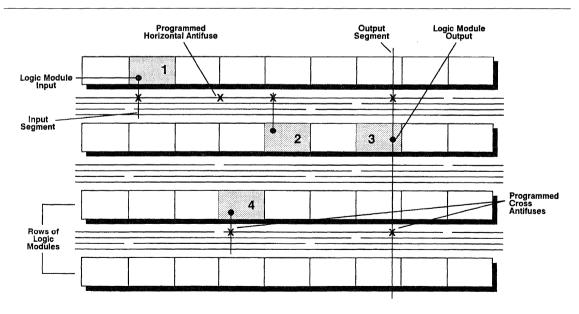

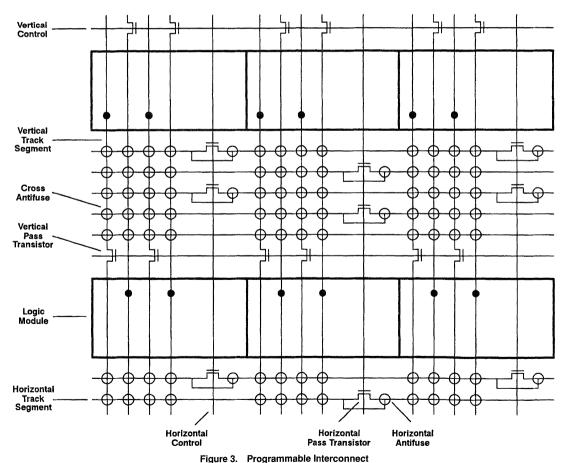

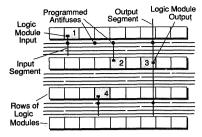

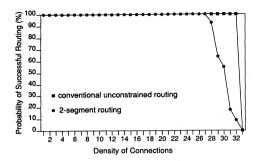

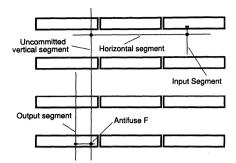

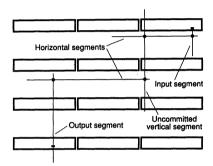

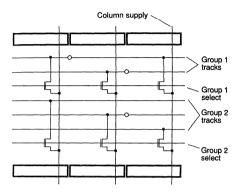

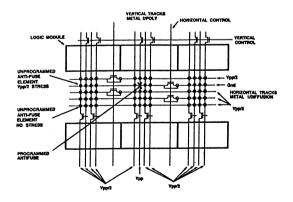

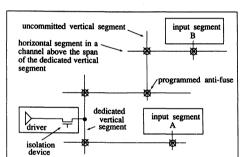

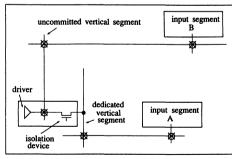

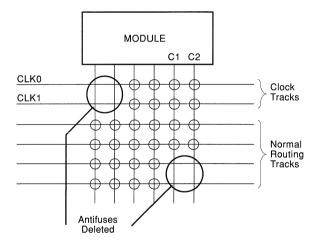

#### Actel's Patented Segmented, Channeled Routing Architecture

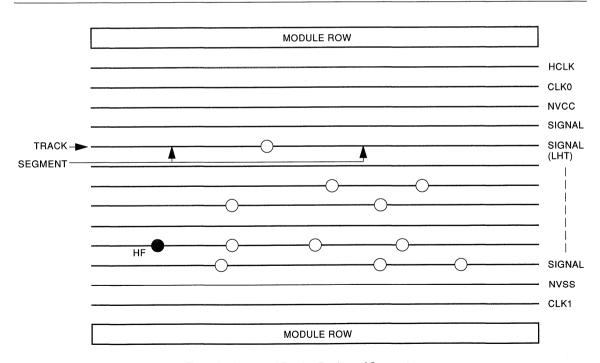

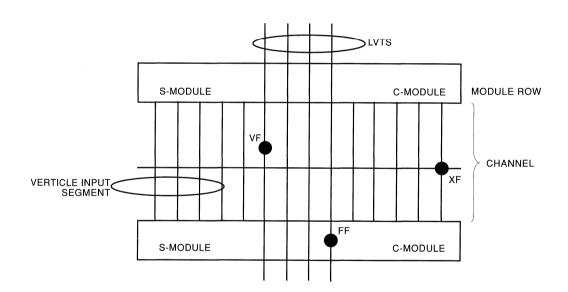

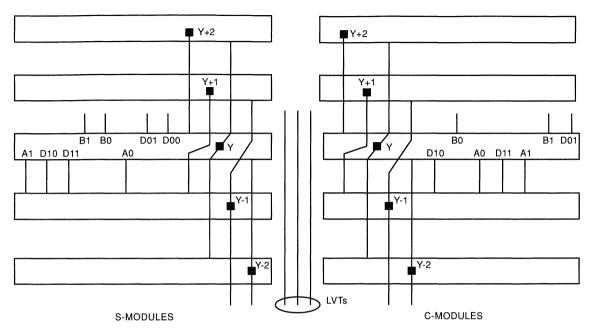

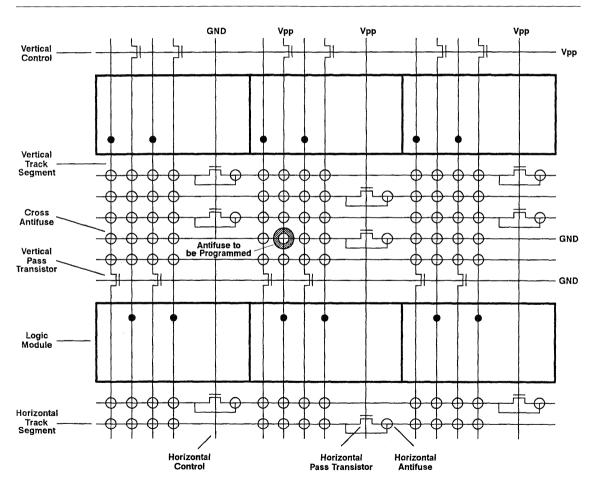

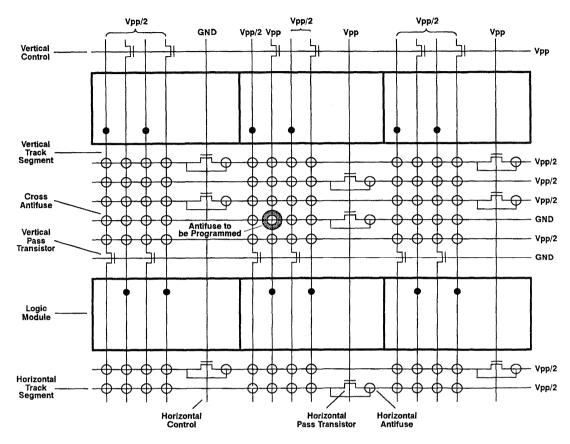

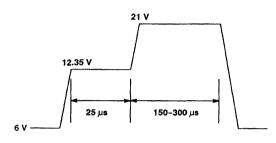

Actel's segmented, channeled routing structure consists of various lengths of routing segments separated by antifuses. Some tracks consist of many short routing segments, while other tracks offer direct interconnect across the chip. Due to the abundant number of routing tracks per channel, a wide variety of segment lengths is offered. These routing tracks can be accessed by programming vertical antifuses located within the metal 1 to

Figure 2. The FPGA Families

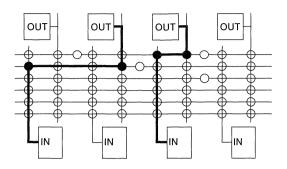

metal 2 vias. See Figure 4 for an example of a typical ACT 1 routing structure.

Figure 4. ACT 1 Routing Example

Actel's segmented routing architecture minimizes the number of antifuses in any path by offering various lengths of interconnect segments. For closely placed modules, short tracks are accessed. For more distant modules, long tracks are accessed. This flexible routing and interconnect architecture ensures that no more than four antifuses are used in any path, with 90 percent of all interconnects requiring only two antifuses.

#### **Highest, Most Predictable Performance**

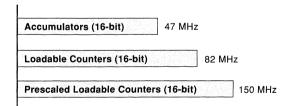

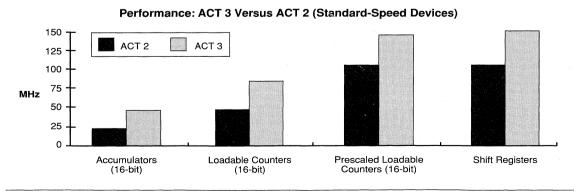

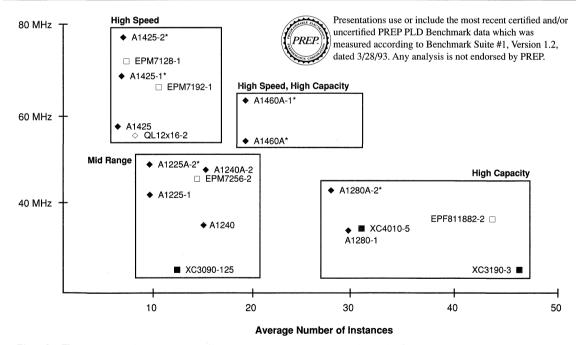

Actel's ACT 3 family offers the highest performance in the FPGA industry: on-chip performance of up to 150 MHz; chip-to-chip speeds over 80 MHz; and 9 ns Clock-to-Out speeds. Figure 5 shows performance of the A1425A-1 per the Programmable Electronics Performance Corporation (PREP<sup>TM</sup>) Benchmarks\*, while using 100% automatic placement and routing tools.

Figure 5. A1425A-1 Performance (Worst-Case Commercial)

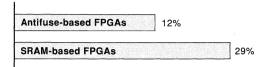

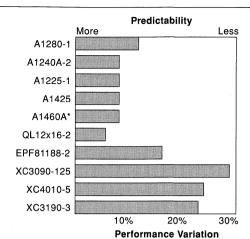

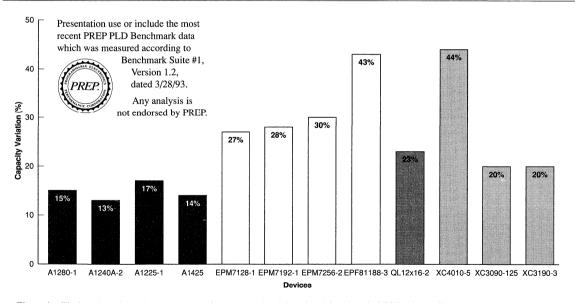

The antifuse-based architectures have also demonstrated very tight distributions in performance. The tighter the distribution, the easier it is to design with. Figure 6 shows the average performance variability of antifuse-based and SRAM-based devices as derived from the PREP benchmarks\* while using 100% automatic placement and routing software. The LOWER

\*All PREP numbers refer to Suite #1, Version 1.2, dated 3-28-93; any analysis is not endorsed by PREP.

the variability, the HIGHER the predictability of your design. Clearly, antifuse-based FPGAs are much more highly predictable than SRAM-based FPGAs.

Figure 6. Performance Variability (LOWER variability means HIGHER predictability and ease-of-design)

This highly predictable performance is directly related to Actel's proprietary PLICE antifuse and segmented, channeled routing architecture. Total capacitance and resistance of each interconnect path has been minimized by:

- · minimizing impedance of the antifuse

- minimizing the number of antifuses per interconnect path (no more than four, 90% of interconnects requiring only two antifuses)

- minimizing the length of the metal tracks used for interconnect For more details on performance and performance predictability, see Section 2, which covers the PREP benchmark results.

#### Actel's Low-Cost Solution

Strong emphasis in process and architectural technologies, along with tight strategic partnerships, allows Actel to offer the most cost-competitive solutions in the programmable logic industry. Actel's technology leadership produces the industry's smallest die sizes for comparable density devices. Actel's strategic partnerships ensure continuous product availability, as well as new product innovation, at industry leading costs. Actel's overall price leadership can be attributed to:

- very small die sizes due to the PLICE antifuse technology

- competitive, multiple foundry fabrication

- · second sourced products

- · leadership in process technology and architectural design

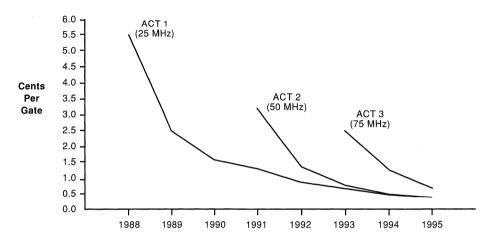

#### **Higher Performance for Lower Cost**

Actel introduced the industry's first antifuse-based programmable architecture in 1988. The small size of the PLICE antifuse has allowed Actel to introduce devices 20% to 50% smaller in die size than comparable competitive devices. Actel's learning curve has been very steep, having manufactured and sold over 3 million FPGAs containing over 750 billion antifuses over the past five years. These economies of scale, paired with technological breakthroughs, have allowed Actel to reduce initial pricing by a magnitude, and to continue to offer higher performance solutions at lower prices (see Figure 7).

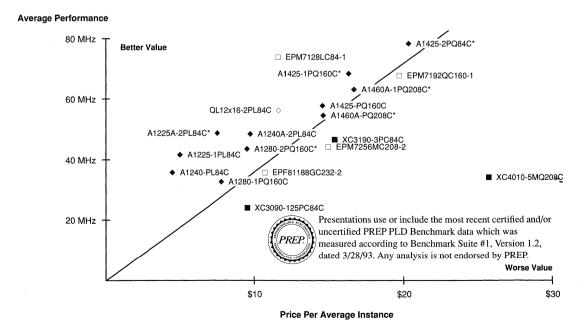

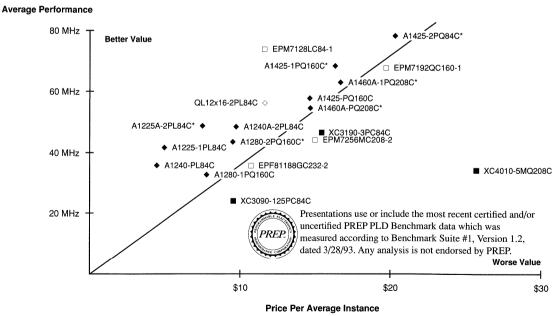

Actel's price leadership has been demonstrated in conjunction with industry standard PREP benchmarks. Actel ACT 2 devices are the best value in the mid-range and high-density classes. In fact, Actel antifuse-based FPGAs represent five of the seven best

value programmable devices based on certified PREP results (see Figure 8).

For more information regarding Actel's value proposition, see the PREP Benchmarks in Section 2.

Figure 7. Actel Families: Cost Per Gate

Figure 8. Price Per Average Instance

#### Actel's High-Density, High-Performance Solution

In 1991, Actel introduced the largest FPGA in the industry, the 8000-gate A1280. In 1993, Actel is introducing the industry's first high-performance, high-density programmable solutions, the A1460A and A14100A. These devices offer up to 10,000 gate array gates and up to 228 user I/Os while delivering on-chip performance to 100 MHz and clock-to-out speeds of 12 nanoseconds (see Table 1).

Table 1. Specifications for A1460A and A14100A

|         | High C          | ensity   | High Per | formance      |

|---------|-----------------|----------|----------|---------------|

|         | Gate<br>Density | User I/O | On-Chip  | Clock-<br>Out |

| A14100A | 10,000          | 228      | 100 MHz  | 12.0 ns       |

| A1460A  | 6,000           | 168      | 100 MHz  | 11.6 ns       |

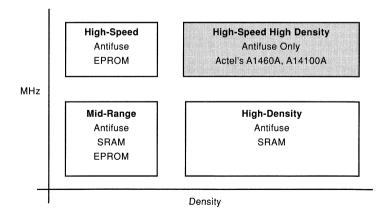

The introduction of the ACT 3 family punctuates the advantages of the antifuse technology. The low impedance of the antifuse supports high-performance designs even at high gate densities. No other programmable technology can offer this combination of high speed and high density (see Figure 9). This combination opens new design possibilities in computers, graphics, high-speed telecommunications and other high-speed and high-I/O applications.

In comparison, EPROM-based architectures offer high performance at low gate densities, but the architecture's performance dwindles and costs rise dramatically as gate capacity increases. The SRAM-based FPGA architectures have been shown to support high-density designs, but are lacking in performance and are quite expensive. Both the lack of performance and the high costs can be attributed to the large size

and electrical characteristics of the SRAM interconnect elements. The small size and low impedance of Actel's antifuse-based architecture offers high speed at high densities, at the fraction of the cost of SRAM devices.

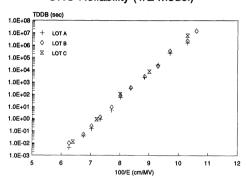

#### **Actel Leads in Reliability**

Actel builds the most reliable field programmable gate arrays (FPGAs) in the industry, with overall reliability ratings of 6 Failures-in-time (FITs at 70°C ambient, 0.9 EV), corresponding to a useful life of more than 40 years. Actel FPGAs have been production proven, 4 million devices shipped to date and over 700 billion antifuses manufactured. The architecture of the devices permits a highly testable structure for routing, logic resources, I/O pads, and programming circuits. As a result, all devices are fully tested prior to shipment, with an outgoing defect level of only 122 ppm. For more details on device reliability and testing, see Section 4.

#### **Actel Offers Fast Flexible Design**

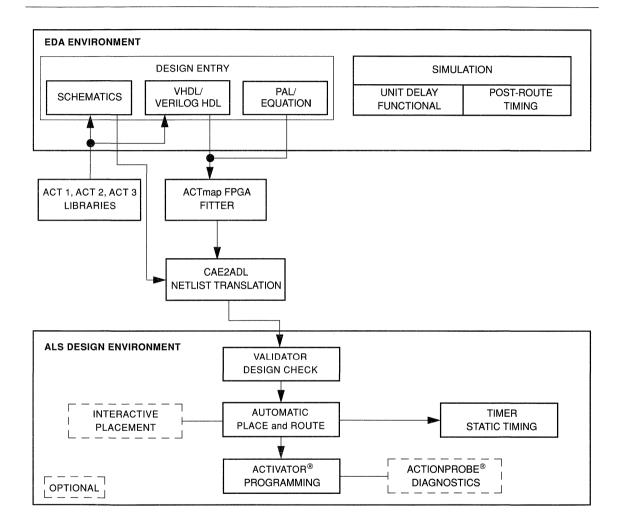

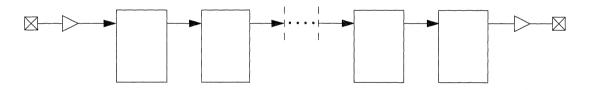

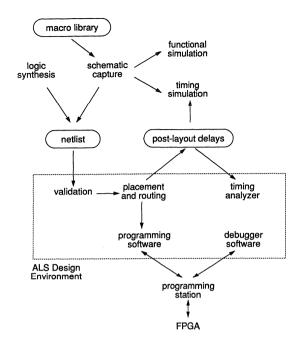

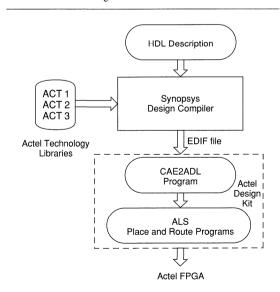

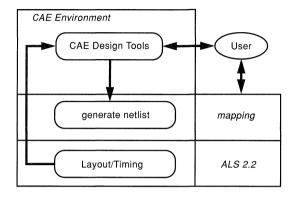

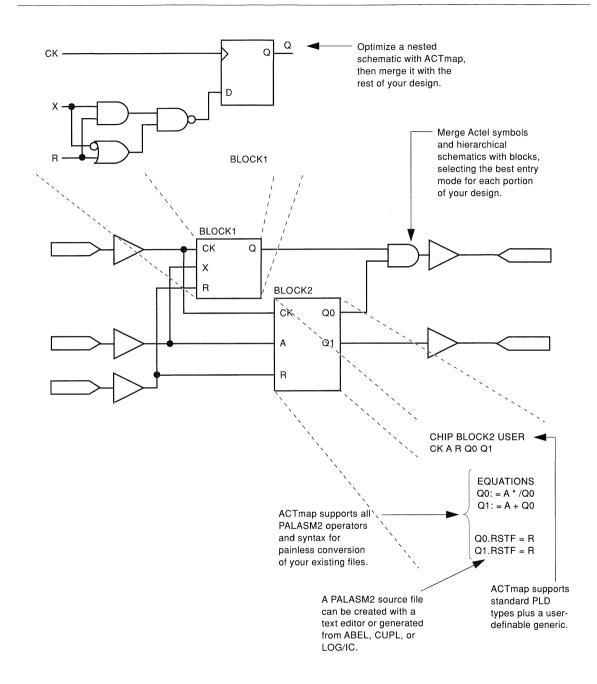

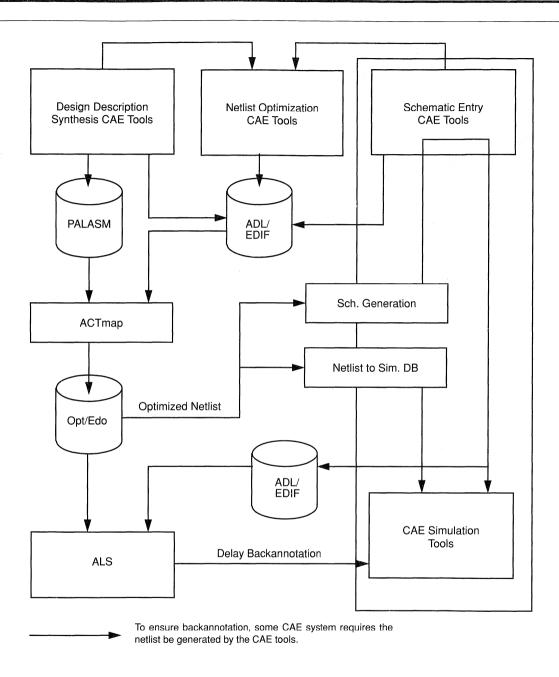

The Actel design flow has been tuned to minimize the effort of bringing designs to market (see Figure 10). A windows-based interface allows users to complete ACT 1, ACT 2, and ACT 3 designs, from concept to silicon, within hours. Compatibility to industry standard design entry tools allows designers to leverage their existing expertise.

The fine granularity of the Actel architecture allows designers to implement simple to complex, random to highly structured designs while using 100% automatic placement and routing tools guaranteeing 80% to 95% gate utilization. Timing analysis software and backannotation simulation allow the designer to quickly verify performance and timing requirements. On-site programming and diagnostic tools provide quick-turn design implementation.

Figure 9. Speed and Density Classifications by Technology

Actel's Designer and Designer Advantage <sup>™</sup> systems support schematic capture, Boolean high-level equation entry, state machine entry, design synthesis input as well as EDIF netlists. The systems offer schematic entry and simulation support for Cadence <sup>™</sup>, Mentor Graphics<sup>®</sup>, OrCAD <sup>™</sup>, and Viewlogic<sup>®</sup>. Additional CAE interfaces are supported through Actel's Industry

Alliance Program, including Data I/O, Intergraph, and MINC. The systems are supported on the following platforms: PC 386/486 and Sun<sup>®</sup> and HP workstations.

For further information regarding Actel's fast, flexible design systems, please see Section 5.

Figure 10. Typical Design Flow for an Actel FPGA

# Component Data

| Product Selector Guide                                  | 1-1   |

|---------------------------------------------------------|-------|

| ACT 1 Field Programmable Gate Arrays                    | 1-3   |

| ACT 2 Field Programmable Gate Arrays                    | 1-31  |

| ACT 3 Field Programmable Gate Arrays                    | 1-79  |

| ACT 1 and ACT 2 Military Field Programmable Gate Arrays | 1-139 |

# **Product Selector Guide**

|          |                  |        |                           | Temp. <sup>3</sup> | User<br>I/O |        | Flip-Flops |       | Equiv. Pkgs. |                |

|----------|------------------|--------|---------------------------|--------------------|-------------|--------|------------|-------|--------------|----------------|

| Device   | Pkg <sup>1</sup> | # Pins | Speed Option <sup>2</sup> |                    |             | Gates  | Dedicated  | Max.  | TTLs         | 20-Pin<br>PALs |

| A1010B   | PL               | 44     | Std, -1, -2               | C, I               | 34          | 1,200  | 0          | 147   | 30           | 12             |

|          | PL               | 68     | Std, -1, -2               | C, I               | 57          | 1,200  | 0          | 147   | 30           | 12             |

|          | VQ               | 80     | Std, -1, -2               | С                  | 57          | 1,200  | 0          | 147   | 30           | 12             |

|          | PQ               | 100    | Std, -1, -2               | C, I               | 57          | 1,200  | 0          | 147   | 30           | 12             |

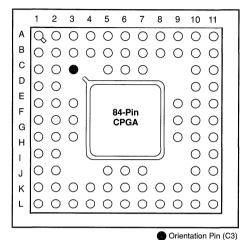

|          | PG               | 84     | Std, -1                   | C, M, B            | 57          | 1,200  | 0          | 147   | 30           | 12             |

| A1020B   | PL               | 44     | Std, -1, -2               | C, I               | 34          | 2,000  | 0          | 273   | 50           | 20             |

|          | PL               | 68     | Std, -1, -2               | C, I               | 57          | 2,000  | 0          | 273   | 50           | 20             |

|          | PL               | 84     | Std, -1, -2               | C, I               | 69          | 2,000  | 0          | 273   | 50           | 20             |

|          | VQ               | 80     | Std, -1, -2               | Ċ                  | 69          | 2,000  | 0          | 273   | 50           | 20             |

|          | PQ               | 100    | Std, -1, -2               | C, I               | 69          | 2,000  | 0          | 273   | 50           | 20             |

|          | PG               | 84     | Std, -1                   | C, M, B            | 69          | 2,000  | 0          | 273   | 50           | 20             |

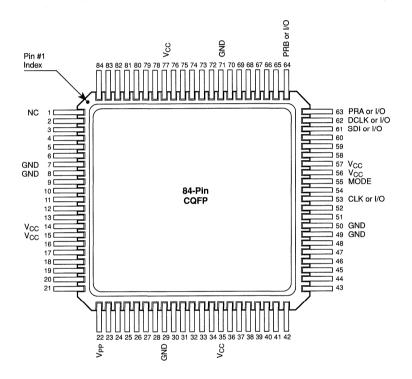

|          | CQ               | 84     | Std, -1**                 | C, M, B, E         | 69          | 2,000  | . 0        | 273   | 50           | 20             |

| A1225A   | PL               | 84     | Std, -1, -2               | C, I               | 72          | 2,500  | 231        | 382   | 63           | 25             |

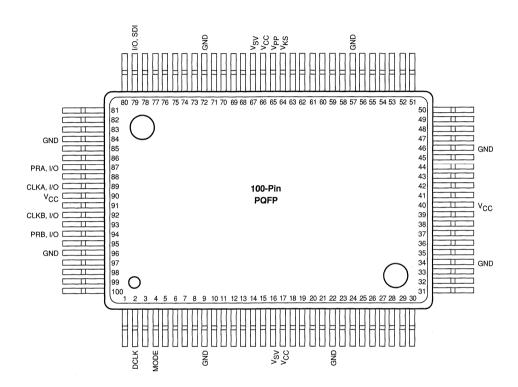

|          | PQ               | 100    | Std, -1, -2               | C, I               | 83          | 2,500  | 231        | 382   | 63           | 25             |

|          | PG               | 100    | Std, -1, -2               | С                  | 83          | 2,500  | 231        | 382   | 63           | 25             |

| A1240A   | PL               | 84     | Std, -1, -2               | C, I               | 72          | 4,000  | 348        | 568   | 100          | 40             |

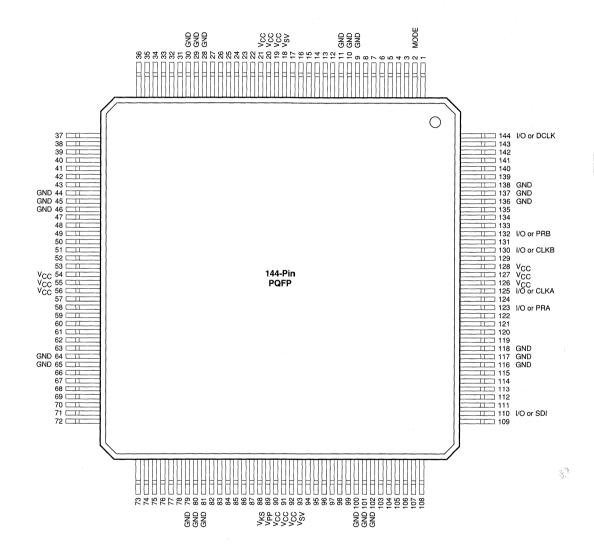

|          | PQ               | 144    | Std, -1, -2               | C, I               | 104         | 4,000  | 348        | 568   | 100          | 40             |

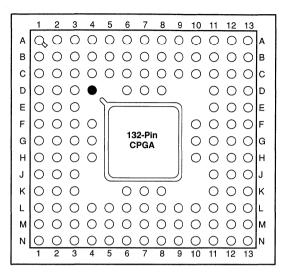

|          | PG               | 132    | Std, -1, -2***            | C, M, B            | 104         | 4,000  | 348        | 568   | 100          | 40             |

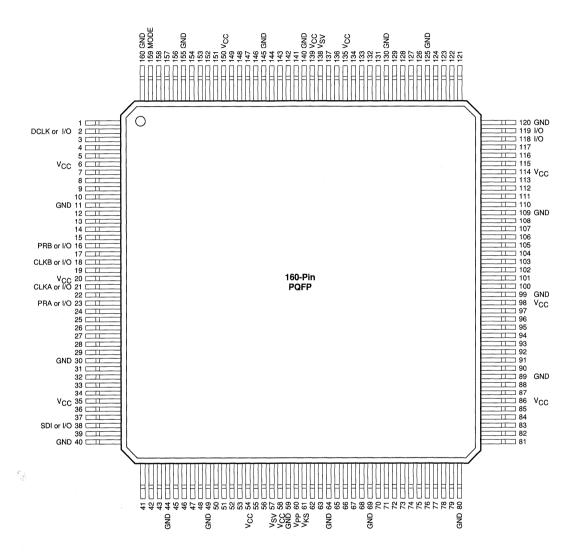

| A1280A   | PQ               | 160    | Std, -1, -2               | C, I               | 125         | 8,000  | 624        | 998   | 200          | 80             |

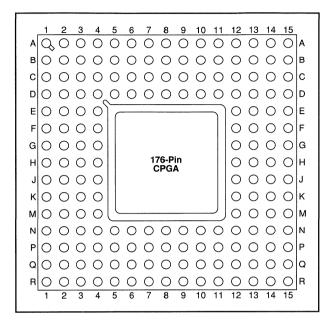

|          | PG               | 176    | Std, -1, -2               | C                  | 140         | 8,000  | 624        | 998   | 200          | 80             |

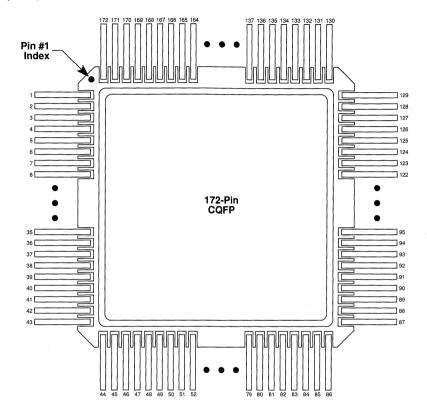

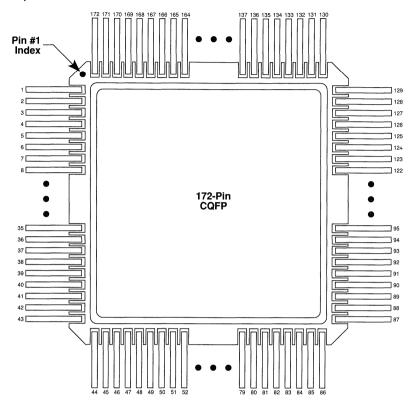

|          | CQ               | 172    | Std, -1**, -2***          | C, M, B, E         | 140         | 8,000  | 624        | 998   | 200          | 80             |

| A1415A*  | PL               | 84     | Std                       | C, I               | 70          | 1,500  | 264        | 312   | 38           | 15             |

|          | PQ               | 100    | Std                       | C, I               | 80          | 1,500  | 264        | 312   | 38           | 15             |

|          | PG               | 100    | Std                       | Ċ                  | 80          | 1,500  | 264        | 312   | 38           | 15             |

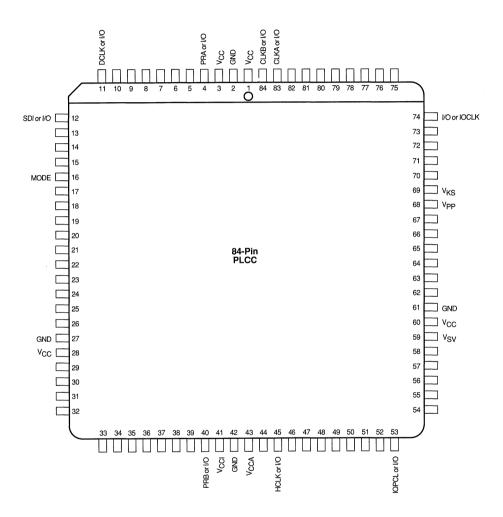

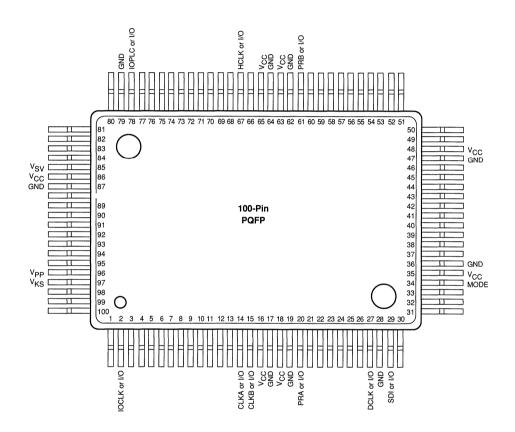

| A1425A*  | PL               | 84     | Std, -1                   | C, I               | 70          | 2,500  | 360        | 435   | 63           | 25             |

|          | PQ               | 100    | Std, -1                   | С, І               | 80          | 2,500  | 360        | 435   | 63           | 25             |

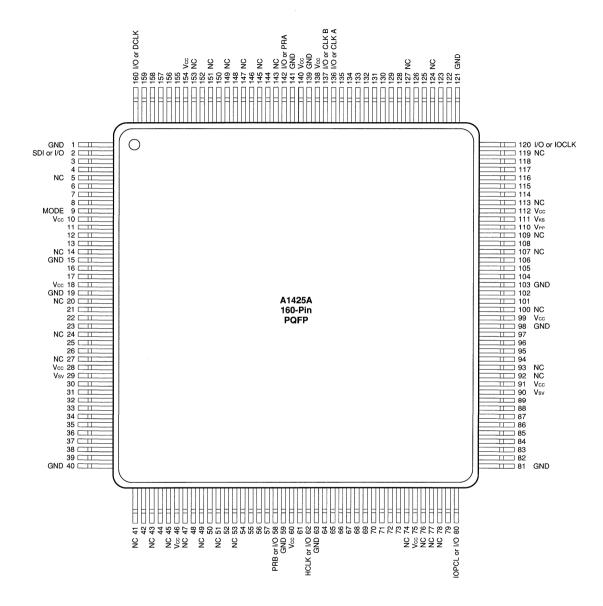

|          | PQ               | 160    | Std, -1                   | C, I               | 100         | 2,500  | 360        | 435   | 63           | 25             |

|          | PG               | 133    | Std, -1***                | C, M, B            | 100         | 2,500  | 360        | 435   | 63           | 25             |

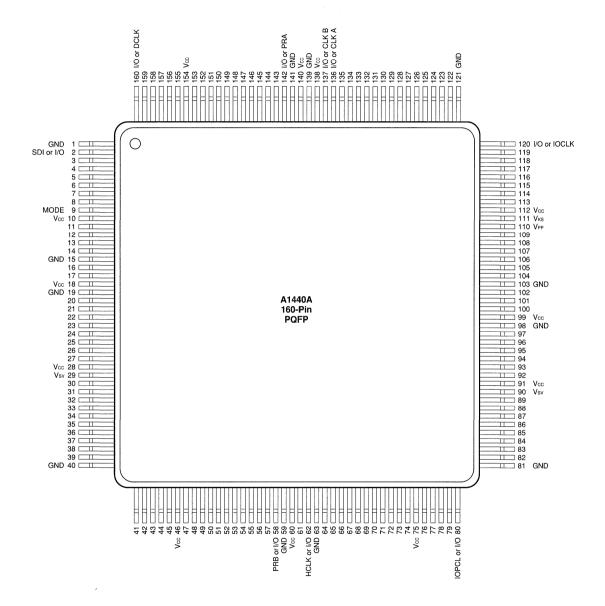

| A1440A*  | PQ               | 160    | Std                       | C, I               | 130         | 4,000  | 568        | 706   | 100          | 40             |

|          | PG               | 175    | Std                       | Ċ                  | 140         | 4,000  | 568        | 706   | 100          | 40             |

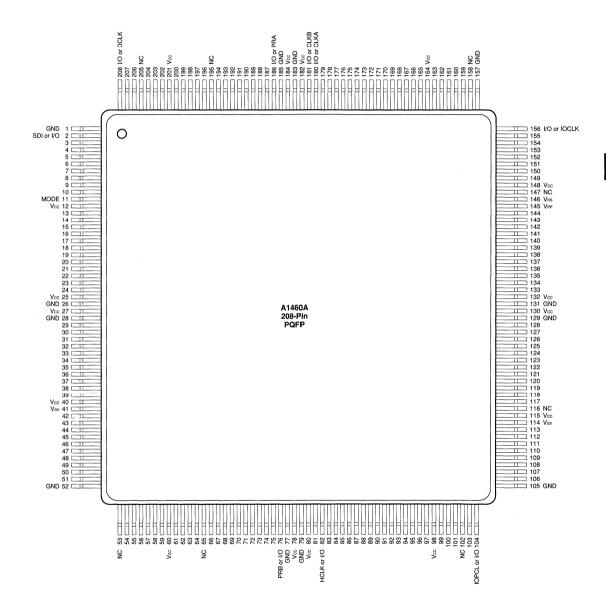

| A1460A*  | PQ               | 208    | Std                       | C, I               | 167         | 6,000  | 768        | 976   | 150          | 60             |

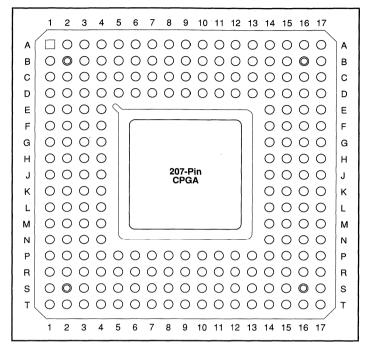

|          | PG               | 207    | Std                       | C, M, B            | 168         | 6,000  | 768        | 976   | 150          | 60             |

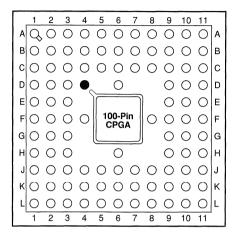

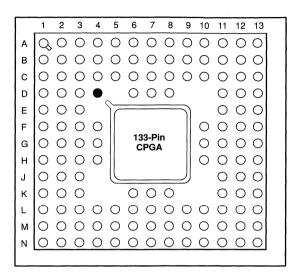

| A14100A* | PG               | 257    | Std                       | C, M, B            | 228         | 10,000 | 1,153      | 1,493 | 250          | 100            |

See below for table notes.

Notes:

1. Package types:

Ceramic Quad Flat Packs Ceramic Pin Grid Arrays Plastic J-Leaded Chip Carriers Plastic Quad Flat Packs Very thin (1.0 mm) Quad Flatpacks CQ PG PL PQ VQ Std -1 -2

Standard Speed 2. Speed Options:

approximately 15% faster than Standard approximately 25% faster than Standard

C 3.Temperature Range:

Commercial Temperature (0 to +75 C) Industrial (-40 to +85 C) Military (-55 to +125 C) MIL-STD-883C Extended Flow

M B E

<sup>\*</sup> Consult Actel for availability

\*\* Extended Flow (E) not offered in –1 Speed

\*\*\* Offered for Commercial (C) devices only

# ACT™ 1 Field Programmable Gate Arrays

#### **Features**

- Up to 2000 Gate Array Gates (6000 PLD equivalent gates)

- Replaces up to 53 TTL Packages

- Replaces up to seventeen 20-Pin PAL<sup>®</sup> Packages

- Design Library with over 250 Macro Functions

- Gate Array Architecture Allows Completely Automatic Place and Route

- Up to 547 Programmable Logic Modules

- Up to 273 Flip-Flops

- Flip-Flop Toggle Rates to 100 MHz

- Two In-Circuit Diagnostic Probe Pins Support Speed Analysis to 25 MHz

- Built-In High Speed Clock Distribution Network

- I/O Drive to 10 mA

- · Nonvolatile, User Programmable

- · Logic Fully Tested Prior to Shipment

#### Description

The ACT™ 1 family of field programmable gate arrays (FPGAs) offers a variety of package, speed, and application combinations. Devices are implemented in silicon gate, 1-micron two-level metal CMOS, and they employ Actel's PLICE® antifuse technology. The unique architecture offers gate array flexibility, high performance, and instant turnaround through user programming. Device utilization is typically 95 percent of available logic modules.

ACT 1 devices also provide system designers with unique on-chip diagnostic probe capabilities, allowing convenient testing and debugging. Additional features include an on-chip clock driver with a hardwired distribution network. The network provides efficient clock distribution with minimum skew.

The user-definable I/Os are capable of driving at both TTL and CMOS drive levels. Available packages include plastic and ceramic J-leaded chip carriers, ceramic and plastic quad flatpacks, and ceramic pin grid array.

A security fuse may be programmed to disable all further programming and to protect the design from being copied or reverse engineered.

#### **Product Family Profile**

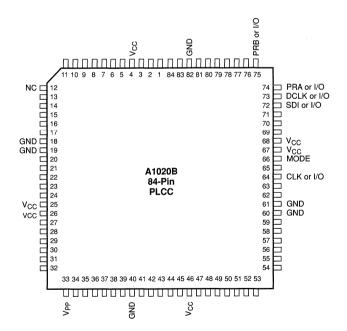

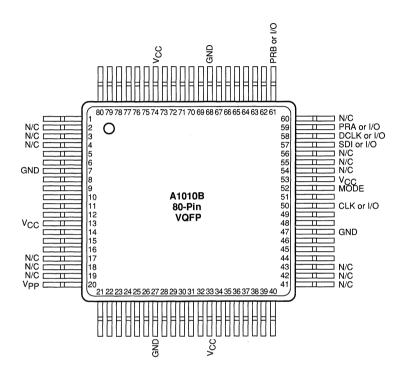

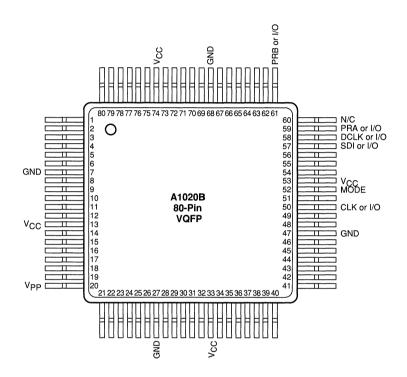

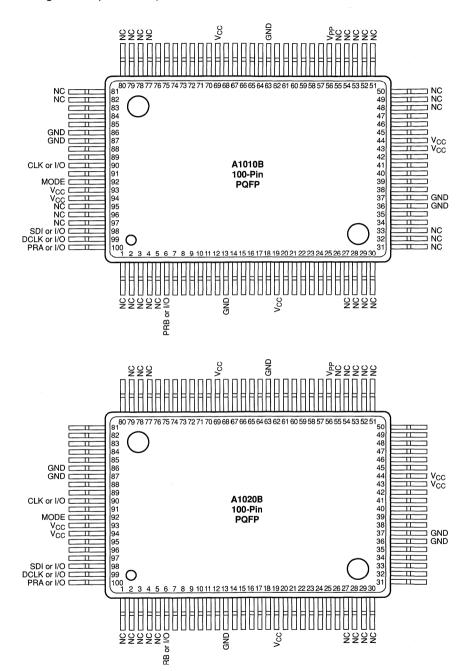

| Device                                                                                              | A1010B                                               | A1020B                                                                     |

|-----------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------|

| Capacity Gate Array Equivalent Gates PLD Equivalent Gates                                           | 1,200<br>3,000                                       | 2,000<br>6,000                                                             |

| TTL Equivalent Packages 20-Pin PAL Equivalent Packages                                              | 30<br>12                                             | 50<br>20                                                                   |

| Logic Modules                                                                                       | 295                                                  | 547                                                                        |

| Flip-Flops (maximum)                                                                                | 147                                                  | 273                                                                        |

| Routing Resources<br>Horizontal Tracks/Channel<br>Vertical Tracks/Column<br>PLICE Antifuse Elements | 22<br>13<br>112,000                                  | 22<br>13<br>186,000                                                        |

| User I/Os (maximum)                                                                                 | 57                                                   | 69                                                                         |

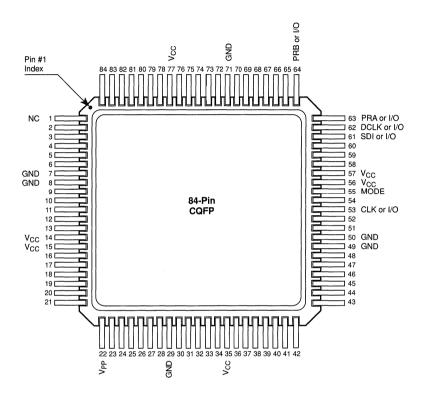

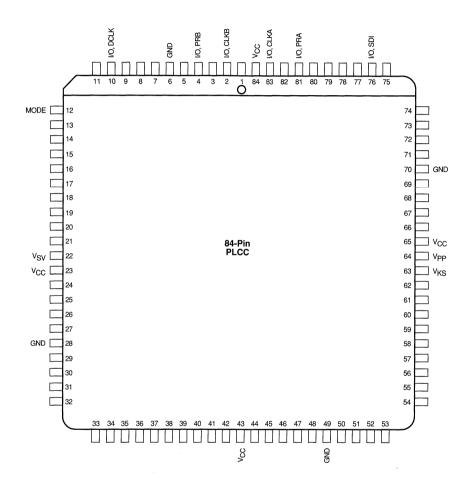

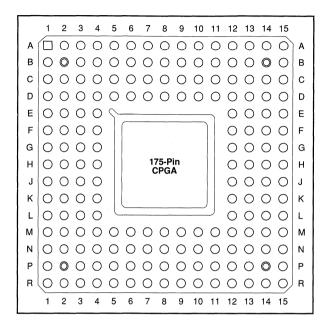

| Packages:                                                                                           | 44 PLCC<br>68 PLCC<br>100 PQFP<br>80 VQFP<br>84 CPGA | 44 PLCC<br>68 PLCC<br>84 PLCC<br>100 PQFP<br>80 VQFP<br>84 CQFP<br>84 CPGA |

| Performance Flip-Flop Toggle Rate (maximum) System Speed (maximum)                                  | 100 MHz<br>40 MHz                                    | 100 MHz<br>40 MHz                                                          |

| CMOS Process                                                                                        | 1.0 μm                                               | 1.0 μm                                                                     |

#### Note:

#### The Designer and Designer Advantage Systems

The ACT 1 device family is supported by Actel's Designer and Designer Advantage Systems, allowing logic design implementation with minimum effort. The systems interface with the resident CAE system to provide a complete gate array design environment: schematic capture, simulation, fully automatic place and route, timing verification, and device programming. The systems are available for  $386/486^{\text{TM}}$  PC and for HP<sup>TM</sup> and Sun workstations and for running Viewlogic®, Mentor Graphics®, Cadence TM, and OrCAD TM.

<sup>1.</sup> See Product Plan on page 1-6 for package availability.

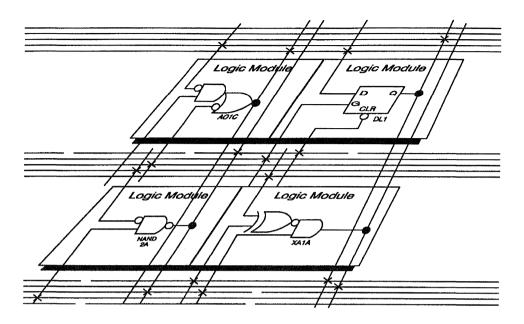

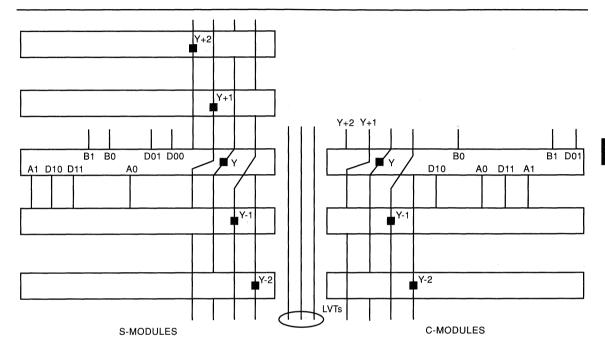

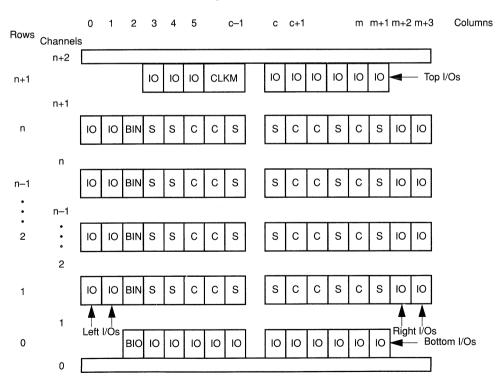

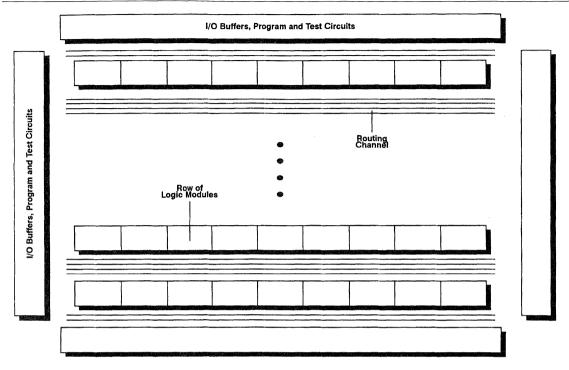

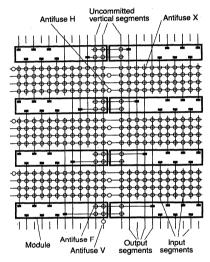

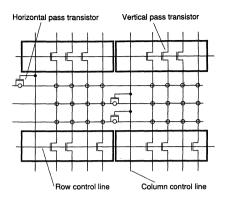

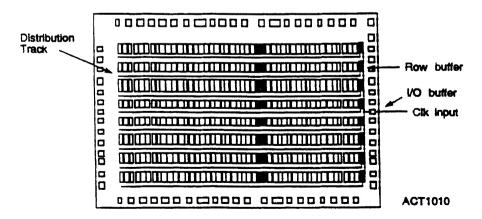

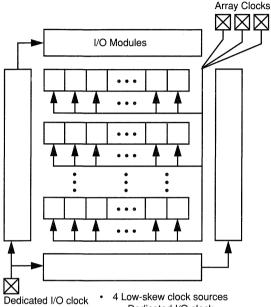

Figure 1. Partial View of an ACT 1 Device

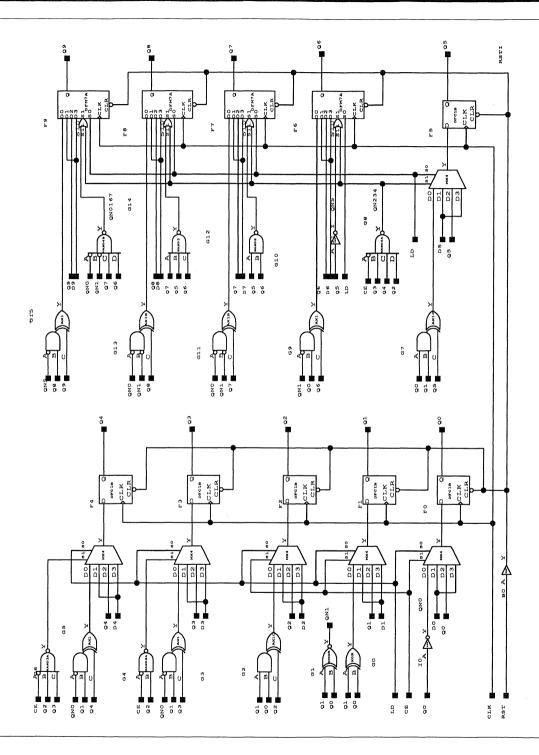

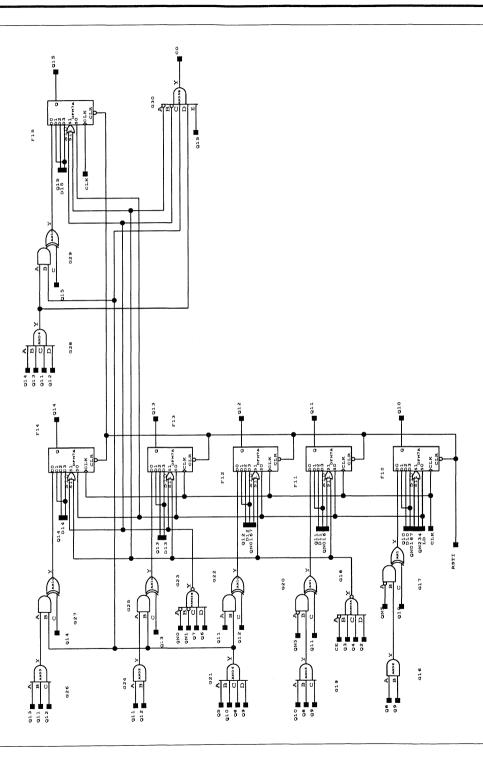

#### **ACT 1 Device Structure**

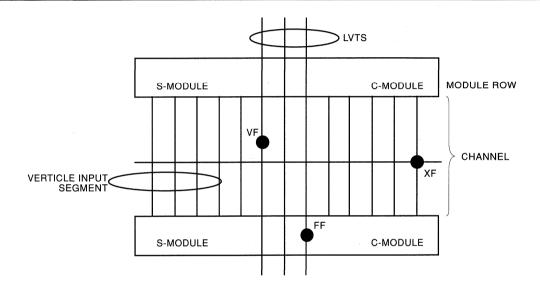

A partial view of an ACT 1 device (Figure 1) depicts four logic modules and distributed horizontal and vertical interconnect tracks. PLICE antifuses, located at intersections of the horizontal and vertical tracks, connect logic module inputs and outputs. During programming, these antifuses are addressed and programmed to make the connections required by the circuit application.

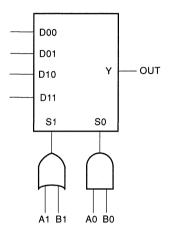

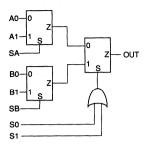

# The ACT 1 Logic Module

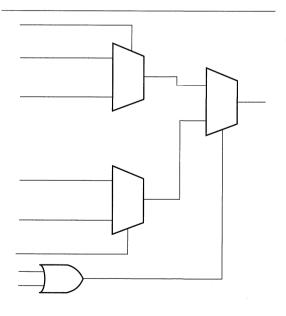

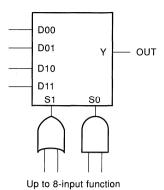

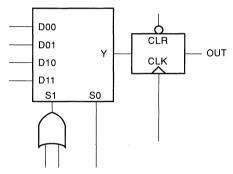

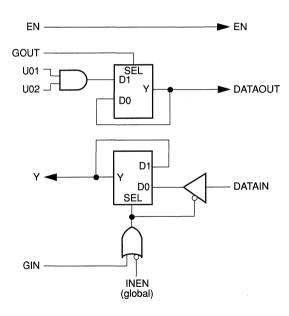

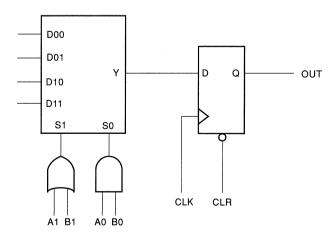

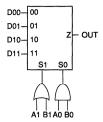

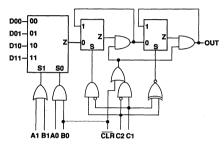

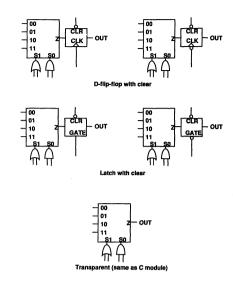

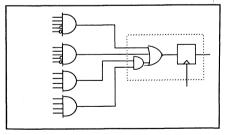

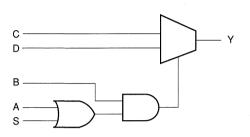

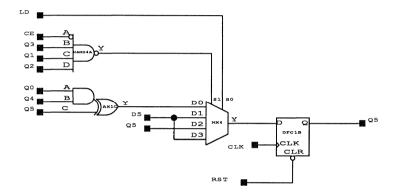

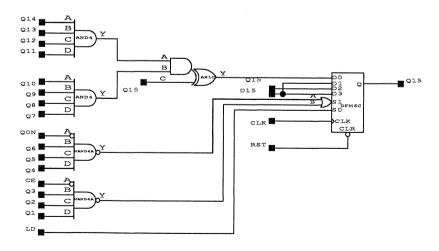

The ACT 1 logic module is an 8-input, one-output logic circuit chosen for the wide range of functions it implements and for its efficient use of interconnect routing resources (Figure 2).

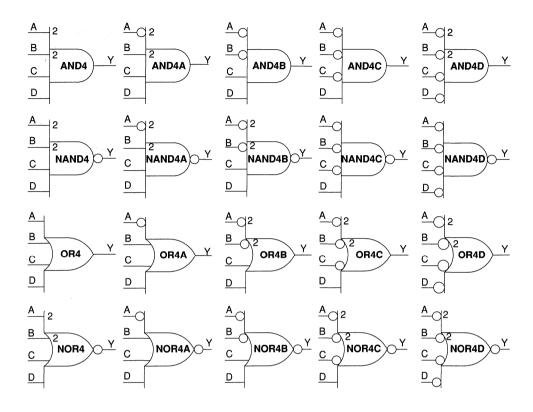

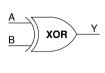

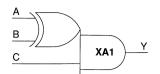

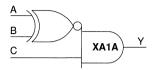

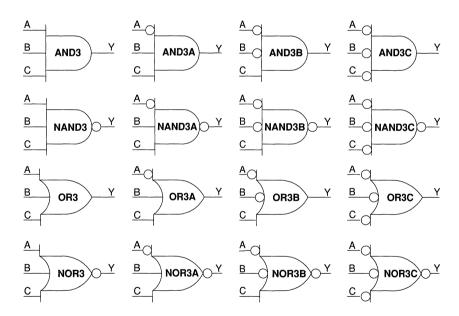

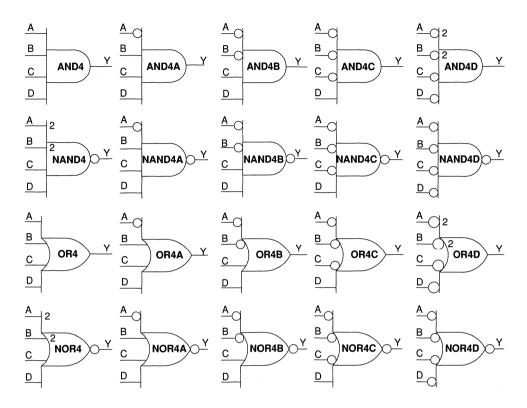

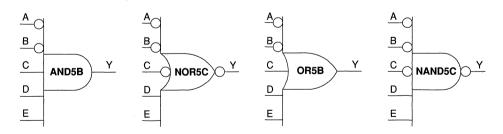

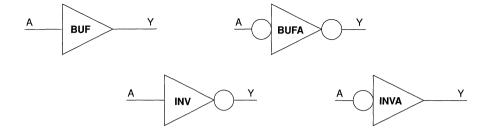

The logic module can implement the four basic logic functions (NAND, AND, OR, and NOR) in gates of two, three, or four inputs. Each function may have many versions, with different combinations of active-low inputs. The logic module can also implement a variety of D-latches, exclusivity functions, AND-ORs, and OR-ANDs. No dedicated hardwired latches or flip-flops are required in the array, since latches and flip-flops may be constructed from logic modules wherever needed in the application.

Figure 2. ACT 1 Logic Module

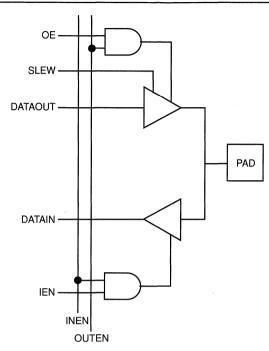

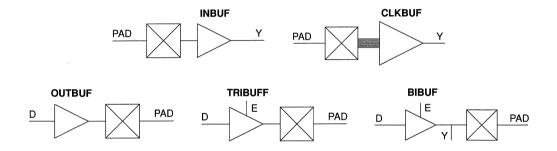

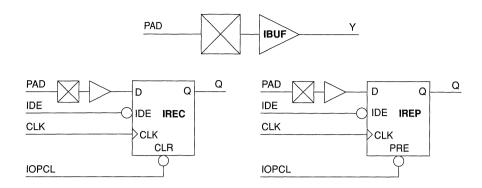

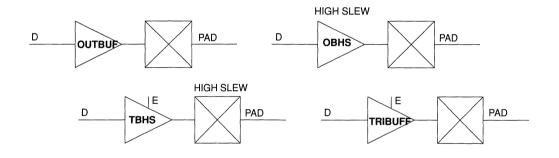

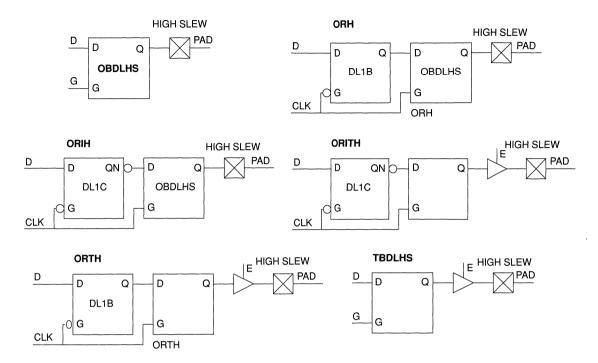

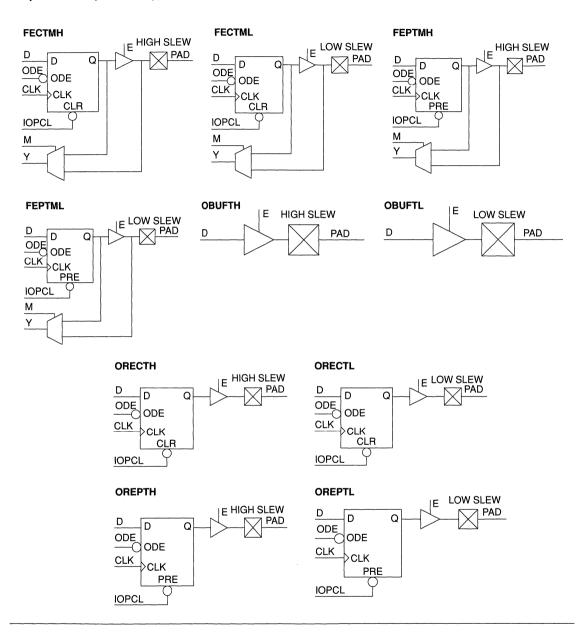

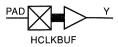

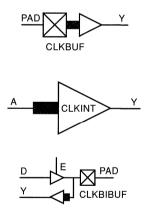

#### I/O Buffers

Each I/O pin is available as an input, output, three-state, or bidirectional buffer. Input and output levels are compatible with standard TTL and CMOS specifications. Outputs sink or source 10 mA at TTL levels. See Electrical Specifications for additional I/O buffer specifications.

#### **Device Organization**

ACT 1 devices consist of a matrix of logic modules arranged in rows separated by wiring channels. This array is surrounded by a ring of peripheral circuits including I/O buffers, testability circuits, and diagnostic probe circuits providing real-time diagnostic capability. Between rows of logic modules are routing channels containing sets of segmented metal tracks with PLICE antifuses. Each channel has 22 signal tracks. Vertical routing is permitted via 13 vertical tracks per logic module column. The resulting network allows arbitrary and flexible interconnections between logic modules and I/O modules.

#### **Probe Pin**

ACT 1 devices have two independent diagnostic probe pins. These pins allow the user to observe any two internal signals by entering the appropriate net name in the diagnostic software. Signals may be viewed on a logic analyzer using Actel's Actionprobe<sup>®</sup> diagnostic tools. The probe pins can also be used as user-defined I/Os when debugging is finished.

## **ACT 1 Array Performance**

#### Temperature and Voltage Effects

Worst-case delays for ACT 1 arrays are calculated in the same manner as for masked array products. A typical delay parameter is multiplied by a derating factor to account for temperature, voltage, and processing effects. However, in an ACT 1 array, temperature and voltage effects are less dramatic than with masked devices. The electrical characteristics of module interconnections on ACT 1 devices remain constant over voltage and temperature fluctuations.

As a result, the total derating factor from typical to worst-case for a standard speed ACT 1 array is only 1.19 to 1, compared to 2 to 1 for a masked gate array.

#### Logic Module Size

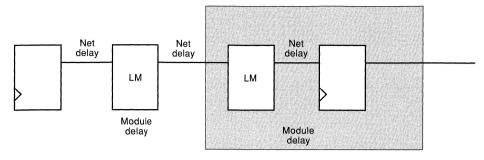

Logic module size also affects performance. A mask programmed gate array cell with four transistors usually implements only one logic level. In the more complex logic module (similar to the complexity of a gate array macro) of an ACT 1 array, implementation of multiple logic levels within a single module is possible. This climinates interlevel wiring and associated RC delays. The effect is termed "net compression."

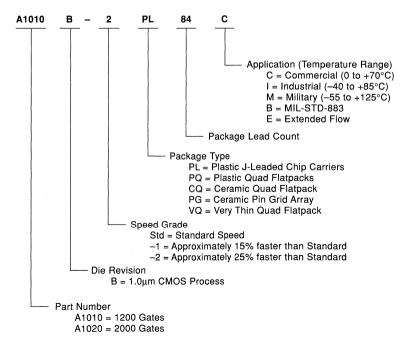

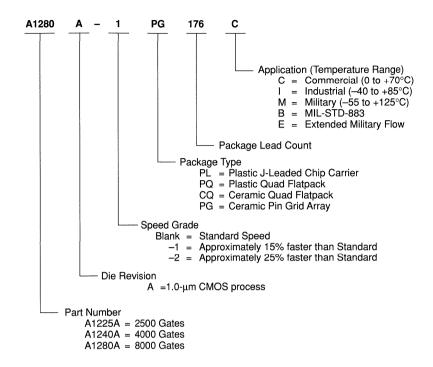

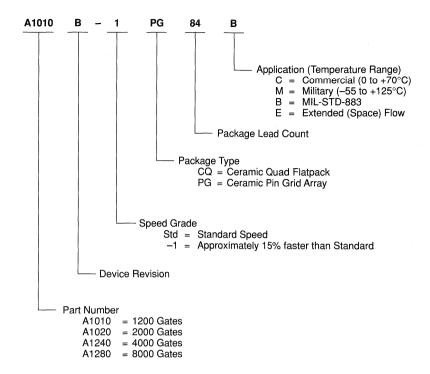

#### Ordering Information

### **Product Plan**

|                                              | Sp       | Speed Grade* Application |          |          | ion      |   |   |   |

|----------------------------------------------|----------|--------------------------|----------|----------|----------|---|---|---|

|                                              | Std      | -1                       | -2       | С        | ı        | М | В | E |

| A1010B Device                                |          |                          |          |          |          |   |   |   |

| 44-pin Plastic Leaded Chip Carrier (PL)      | ~        | ~                        | V        | ~        | ~        |   |   |   |

| 68-pin Plastic Leaded Chip Carrier (PL)      | <b>✓</b> | ~                        | <b>✓</b> | ~        | ~        |   |   | _ |

| 100-pin Plastic Quad Flatpack (PQ)           | <b>~</b> | ~                        | <b>✓</b> | ~        | ~        |   |   |   |

| 80-pin Very Thin (1.0 mm) Quad Flatpack (VQ) | Р        | Р                        | Р        | Р        |          |   |   |   |

| 84-pin Ceramic Pin Grid Array (PG)           | ~        | ~                        |          | ~        | _        | ~ | ~ | _ |

| A1020B Device                                |          |                          |          |          |          |   |   |   |

| 44-pin Plastic Leaded Chip Carrier (PL)      | ~        | ~                        | ~        | ~        |          |   |   | _ |

| 68-pin Plastic Leaded Chip Carrier (PL)      | <b>V</b> | ~                        | <b>✓</b> | ~        | <b>~</b> | _ |   | _ |

| 84-pin Plastic Leaded Chip Carrier (PL)      |          | ~                        | <b>V</b> | <b>✓</b> | ~        |   |   |   |

| 100-pin Plastic Quad Flatpack (PQ)           |          | <b>✓</b>                 | <b>V</b> | <b>/</b> | <b>✓</b> |   |   |   |

| 80-pin Very Thin (1.0 mm) Quad Flatpack (VQ) | Р        | Р                        | Р        | Р        |          | _ | _ | _ |

| 84-pin Ceramic Pin Grid Árray (PG)           | <b>✓</b> | ~                        | _        | ~        | _        | ~ | ~ |   |

| 84-pin Ceramic Quad Flatpack (CQ)            | <b>/</b> | ~                        |          | ~        |          | ~ | ~ | ~ |

Applications:

C = Commercial

Availability:

✓ = Available

P = Planned

\* Speed Grade: -1 = Approx. 15% faster than Standard -2 = Approx. 25% faster than Standard

I = Industrial

M = Military

B = MIL-STD-883 E = Extended Flow

- = Not Planned

### **Device Resources**

|        |               | -     | User I/Os |        |        |        |         |  |

|--------|---------------|-------|-----------|--------|--------|--------|---------|--|

| Device | Logic Modules | Gates | 44-pin    | 68-pin | 80-pin | 84-pin | 100-pin |  |

| A1010B | 295           | 1200  | 34        | 57     | 57     | 57     | 57      |  |

| A1020B | 547           | 2000  | 34        | 57     | 69     | 69     | 69      |  |

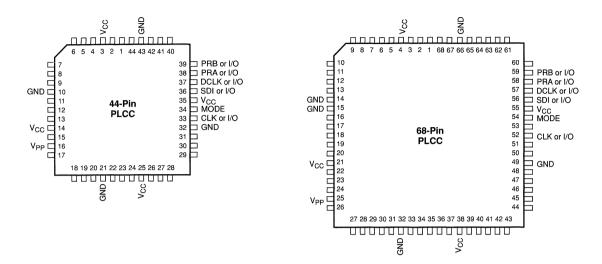

#### Pin Description

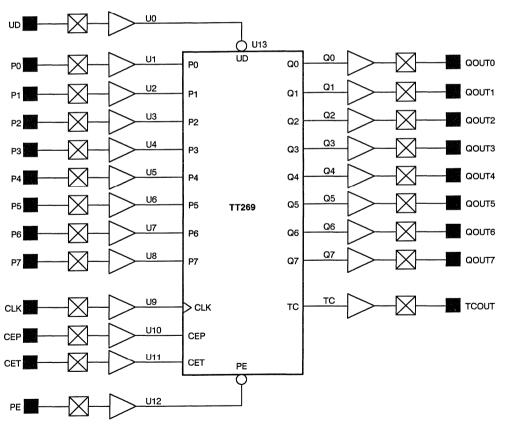

#### CLK Clock (Input)

TTL Clock input for global clock distribution network. The Clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.

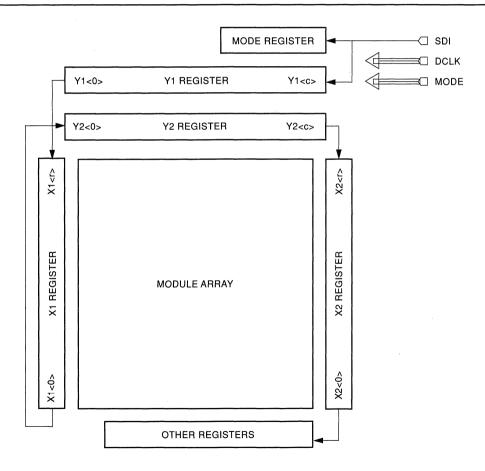

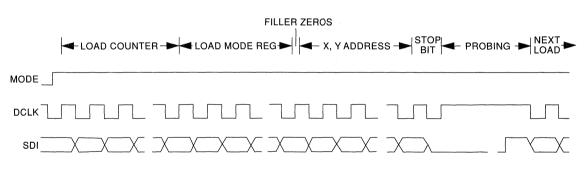

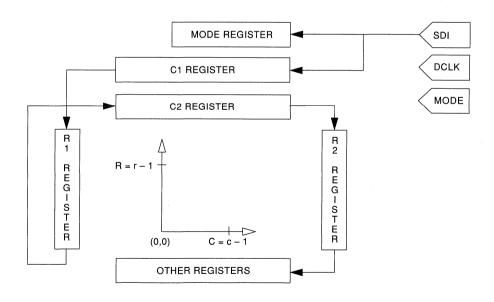

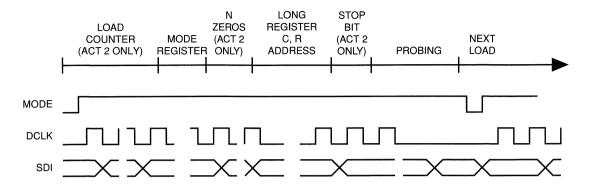

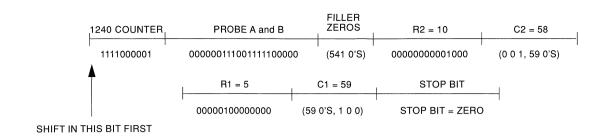

#### DCLK Diagnostic Clock (Input)

TTL Clock input for diagnostic probe and device programming. DCLK is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### GND Ground

Input LOW supply voltage.

#### I/O Input/Output (Input, Output)

I/O pin functions as an input, output, three-state, or bidirectional buffer. Input and output levels are compatible with standard TTL and CMOS specifications. Unused I/O pins are automatically driven LOW by the ALS software.

#### MODE Mode (Input)

The MODE pin controls the use of multifunction pins (DCLK, PRA, PRB, SDI). When the MODE pin is HIGH, the special functions are active. When the MODE pin is LOW, the pins function as I/O.

#### NC No Connection

This pin is not connected to circuitry within the device.

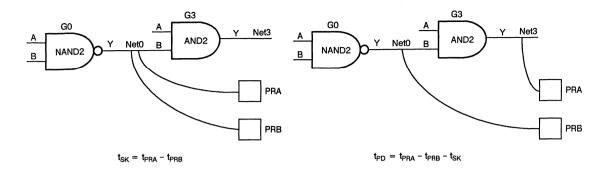

#### PRA Probe A (Output)

The Probe A pin is used to output data from any user-defined design node within the device. This independent diagnostic pin is

used in conjunction with the Probe B pin to allow real-time diagnostic output of any signal path within the device. The Probe A pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect the programmed design's confidentiality. PRA is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### PRB Probe B (Output)

The Probe B pin is used to output data from any user-defined design node within the device. This independent diagnostic pin is used in conjunction with the Probe A pin to allow real-time diagnostic output of any signal path within the device. The Probe B pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect the programmed design's confidentiality. PRB is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### SDI Serial Data Input (Input)

Serial data input for diagnostic probe and device programming. SDI is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### V<sub>CC</sub> Supply Voltage

Input HIGH supply voltage.

#### V<sub>PP</sub> Programming Voltage

Input supply voltage used for device programming. This pin must be connected to  $V_{CC}$  during normal operation.

## Absolute Maximum Ratings1 Free air temperature range

| Symbol           | Parameter                               | Limits                       | Units |

|------------------|-----------------------------------------|------------------------------|-------|

| V <sub>CC</sub>  | DC Supply Voltage <sup>2</sup>          | -0.5 to +7.0                 | Volts |

| VI               | Input Voltage                           | –0.5 to $V_{\rm CC}$ +0.5    | Volts |

| Vo               | Output Voltage                          | $-0.5$ to V $_{\rm CC}$ +0.5 | Volts |

| I <sub>IO</sub>  | I/O Sink/Source<br>Current <sup>3</sup> | ±20                          | mA    |

| T <sub>STG</sub> | Storage Temperature                     | -65 to +150                  | °C    |

#### Note:

- 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Device should not be operated outside the Recommended Operating Conditions.

- V<sub>PP</sub> = V<sub>CC</sub>, except during device programming.

Device inputs are normally high impedance and draw extremely low current. However, when input voltage is greater than V<sub>CC</sub> + 0.5 V or less than GND 0.5 V, the internal protection diode will be forward biased and can draw excessive current.

## **Recommended Operating Conditions**

| Parameter                         | Commercial | Industrial | Military    | Units            |

|-----------------------------------|------------|------------|-------------|------------------|

| Temperature<br>Range <sup>1</sup> | 0 to +70   | -40 to +85 | -55 to +125 | °C               |

| Power Supply<br>Tolerance         | ±5         | ±10        | ±10         | %V <sub>CC</sub> |

#### Note:

1. Ambient temperature  $(T_A)$  used for commercial and industrial; case temperature  $(T_C)$  used for military.

## **Electrical Specifications**

| Symbol                                        | Parameter                                       | Com  | mercial               | Industrial |                       | М    | ilitary               | Units |

|-----------------------------------------------|-------------------------------------------------|------|-----------------------|------------|-----------------------|------|-----------------------|-------|

| Symbol                                        | rarameter                                       | Min. | Max.                  | Min.       | Max.                  | Min. | Max.                  | Units |

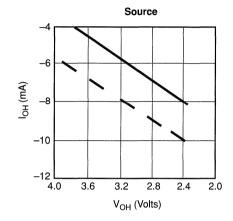

| V <sub>OH</sub> <sup>1</sup>                  | $(I_{OH} = -10 \text{ mA})^2$                   | 2.4  |                       |            |                       |      |                       | V     |

|                                               | $(I_{OH} = -6 \text{ mA})$                      | 3.84 |                       |            |                       |      |                       | ٧     |

|                                               | $(I_{OH} = -4 \text{ mA})$                      |      |                       | 3.7        |                       | 3.7  |                       | ٧     |

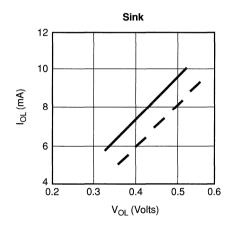

| V <sub>OL</sub> <sup>1</sup>                  | $(I_{OL} = 10 \text{ mA})^2$                    |      | 0.5                   |            |                       | -    |                       | V     |

|                                               | (I <sub>OL</sub> = 6 mA)                        |      | 0.33                  |            | 0.40                  |      | 0.40                  | ٧     |

| V <sub>IL</sub>                               |                                                 | -0.3 | 0.8                   | -0.3       | 0.8                   | -0.3 | 0.8                   | ٧     |

| V <sub>IH</sub>                               |                                                 | 2.0  | V <sub>CC</sub> + 0.3 | 2.0        | V <sub>CC</sub> + 0.3 | 2.0  | V <sub>CC</sub> + 0.3 | ٧     |

| Input Transition Ti                           | me t <sub>R</sub> , t <sub>F</sub> <sup>2</sup> |      | 500                   |            | 500                   | -    | 500                   | ns    |

| C <sub>IO</sub> I/O Capacitan                 | ce <sup>2, 3</sup>                              |      | 10                    |            | 10                    |      | 10                    | pF    |

| Standby Current, I <sub>CC</sub> <sup>4</sup> |                                                 |      | 3                     |            | 10                    |      | 20                    | mA    |

| Leakage Current <sup>5</sup>                  |                                                 | -10  | 10                    | -10        | 10                    | -10  | 10                    | μΑ    |

| I <sub>OS</sub> Output Short                  | $(V_O = V_{CC})$                                |      | 140                   |            | 140                   |      | 140                   | mA    |

| Circuit Current <sup>6</sup>                  | (V <sub>O</sub> = GND)                          |      | -100                  |            | -100                  |      | -100                  | mA    |

#### Notes:

- 1. Only one output tested at a time.  $V_{CC} = min$ .

- 2. Not tested, for information only.

- 3. Includes worst-case 84-pin PLCC package capacitance.  $V_{OUT} = 0 \text{ V}$ , f = 1 MHz.

- 4. Typical standby current = 1 mA. All outputs unloaded. All inputs = V<sub>CC</sub> or GND.

- 5.  $V_O$ ,  $V_{IN} = V_{CC}$  or GND.

- 6. Only one output tested at a time. Min. at  $V_{CC} = 4.5 \text{ V}$ ; Max. at  $V_{CC} = 5.5 \text{ V}$ .

#### **Package Thermal Characteristics**

The device junction to case thermal characteristics is  $\theta$ jc, and the junction to ambient air characteristics is  $\theta$ ja. The thermal characteristics for  $\theta$ ja are shown with two different air flow rates.

Maximum junction temperature is 150°C.

A sample calculation of the maximum power dissipation for an 84-pin plastic leaded chip carrier at commercial temperature is as follows:

$$\frac{\text{Max junction temp. (°C) - Max commercial temp. (°C)}}{\theta \text{ja (°C/W)}} = \frac{150^{\circ}\text{C} - 70^{\circ}\text{C}}{44^{\circ}\text{C/W}} = 1.82 \text{ W}$$

| Package Type                     | Pin Count | θјс | θja<br>Still Air | θja<br>300 ft/min | Units |

|----------------------------------|-----------|-----|------------------|-------------------|-------|

| Plastic J-Leaded Chip Carrier    | 44        | 15  | 52               | 40                | °C/W  |

| •                                | 68        | 13  | 45               | 35                | °C/W  |

|                                  | 84        | 12  | 44               | 33                | °C/W  |

| Plastic Quad Flatpack            | 100       | 13  | 55               | 47                | °C/W  |

| Very Thin (1.0 mm) Quad Flatpack | 80        | 12  | 68               | 55                | °C/W  |

| Ceramic Pin Grid Array           | 84        | 8   | 33               | 20                | °C/W  |

| Ceramic Quad Flatpack            | 84        | 5   | 40               | 30                | °C/W  |

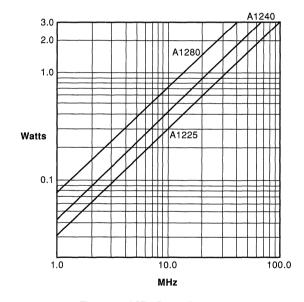

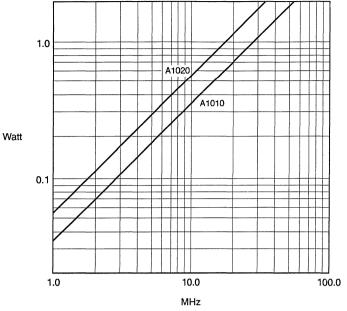

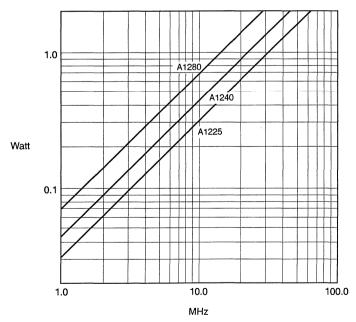

#### **Power Dissipation**

The following formula is used to calculate total device dissipation.

Total Device Power (mW) = (0.20 x N x F1) + (0.085 x M x F2) + (0.80 x P x F3)

#### Where:

F1 = Average logic module switching rate in MHz

F2 = CLKBUF macro switching rate in MHz

F3 = Average I/O module switching rate in MHz

M = Number of logic modules connected to the CLKBUF macro

N = Total number of logic modules used in the design (including M)

P = Number of outputs loaded with 50 pF

Average switching rate of logic modules and of I/O modules is some fraction of the device operating frequency (usually CLKBUF). Logic modules and I/O modules switch states (from low-to-high or from high-to-low) only if the input data changes when the module is enabled. A conservative estimate for average

logic module and I/O module switching rates (variables F1 and F3, respectively) is 10% of device clock driver frequency.

If the CLKBUF macro is not used in the design, eliminate the second term (including F2 and M variables) from the formula.

#### Sample A1020 Device Power Calculation

To illustrate the power calculation, consider a large design operating at high frequency. This sample design utilizes 85% of available logic modules on the A1020-series device (.85 x 547 = 465 logic modules used). The design contains 104 flip-flops (208 logic modules). Operating frequency of the design is 16 MHz. In this design, the CLKBUF macro drives the clock network. Logic modules and I/O modules are switching states at approximately 10% of the clock frequency rate (.10 x 16 MHz = 1.6 MHz). Sixteen outputs are loaded with 50 pF.

To summarize the design described above: N=465; M=208; F2=16; F1=4; F3=4; P=16. Total device power can be calculated by substituting these values for variables in the device dissipation formula.

Total device power for this example =

$(0.20 \times 465 \times 1.6) + (0.085 \times 208 \times 16) + (0.80 \times 16 \times 1.6) = 452 \text{ mW}$

## **Functional Timing Tests**

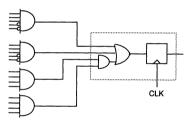

AC timing for logic module internal delays is determined after place and route. The ALS Timer utility displays actual timing parameters for circuit delays. ACT 1 devices are AC tested to a "binning" circuit specification.

The circuit consists of one input buffer  $+ n \log n \mod n + n \log n \mod n$  output buffer (n = 16 for A1010B; n = 28 for A1020B). The logic

modules are distributed along two sides of the device, as inverting or non-inverting buffers. The modules are connected through programmed antifuses with typical capacitive loading.

Propagation delay [ $t_{PD} = (t_{PLH} + t_{PHL})/2$ ] is tested to the following AC test specifications.

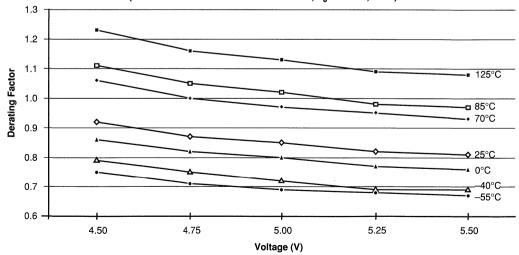

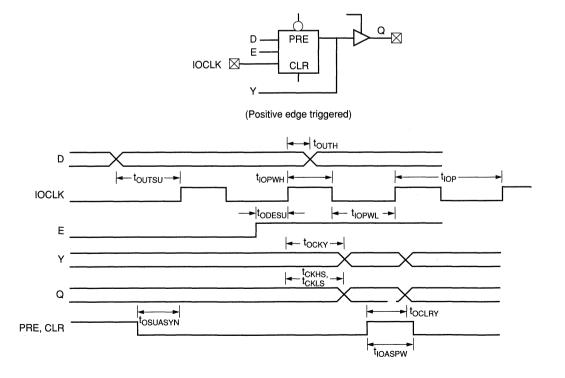

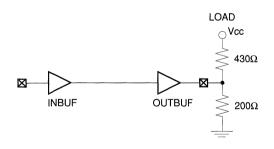

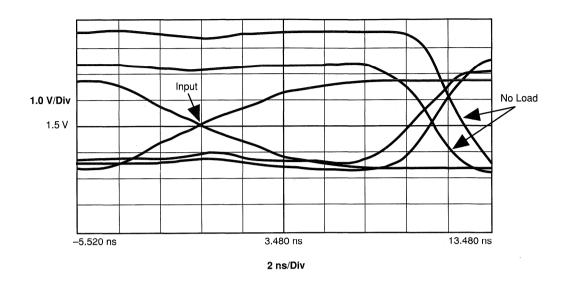

### **Output Buffer Performance Derating**

Military, worst-case values at 125°C, 4.5 V.

Commercial, worst-case values at 70°c, 4.75 V.

#### Note:

The above curves are based on characterizations of sample devices and are not completely tested on all devices.

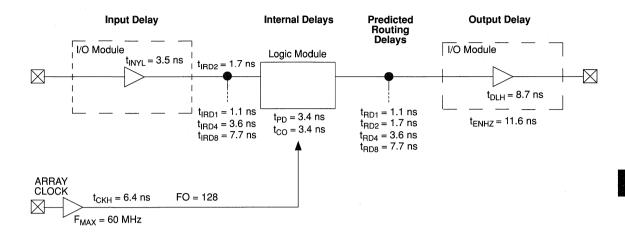

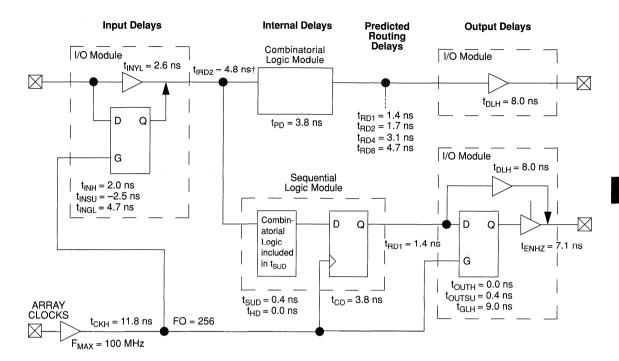

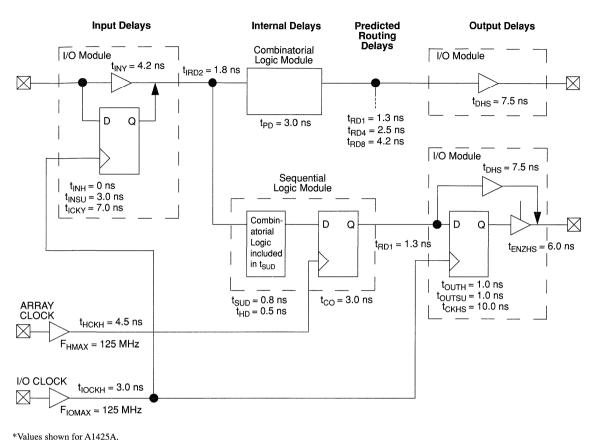

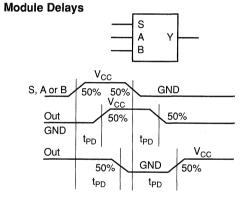

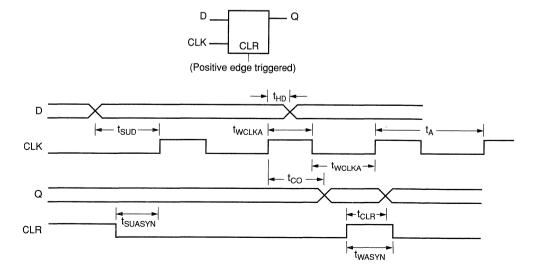

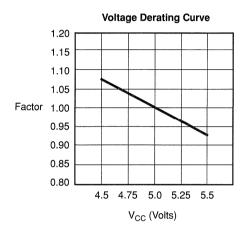

#### **ACT 1 Timing Model\***

<sup>\*</sup>Values shown for ACT 1 '-2' speed devices at worst-case commercial conditions.

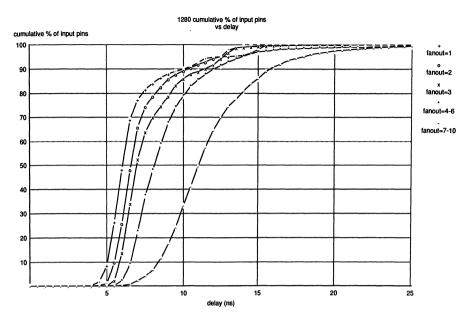

# Predictable Performance: Tight Delay Distributions

Propagation delay between logic modules depends on the resistive and capacitive loading of the routing tracks, the interconnect elements, and the module inputs being driven. Propagation delay increases as the length of routing tracks, the number of interconnect elements, or the number of inputs increases.

From a design perspective, the propagation delay can be statistically correlated or modeled by the fanout (number of loads) driven by a module. Higher fanout usually requires some paths to have longer routing tracks.

The ACT 1 family delivers a very tight fanout delay distribution. This tight distribution is achieved in two ways: by decreasing the delay of the interconnect elements and by decreasing the number of interconnect elements per path.

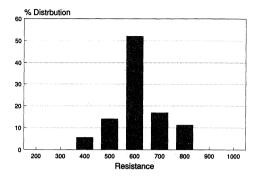

Actel's patented PLICE antifuse offers a very low resistive/capacitive interconnect. The ACT 1 family's antifuses, fabricated in 1.0 µm lithography, offer nominal levels of 500 ohms resistance and 7.5 femtofarad (fF) capacitance per antifuse.

The ACT 1 fanout distribution is also tight due to the low number of antifuses required for each interconnect path. The ACT 1 family's proprietary architecture limits the number of antifuses per path to a maximum of four, with 90% of interconnects using two antifuses.

Logic Module + Routing Delay, by Fanout (ns) (Worst-Case Commercial Conditions)

| Family     | FO=1 | FO=2 | FO=3 | FO=4 | FO=8 |

|------------|------|------|------|------|------|

| 'STD'      | 5.9  | 6.7  | 7.8  | 9.3  | 14.7 |

| '-1' speed | 5.0  | 5.7  | 6.6  | 7.9  | 12.5 |

| '-2' speed | 4.5  | 5.1  | 5.9  | 7.0  | 11.1 |

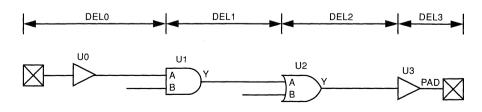

#### Timing Characteristics

Timing characteristics for ACT 1 devices fall into three categories: family dependent, device dependent, and design dependent. The input and output buffer characteristics are common to all ACT 1 family members. Internal routing delays are device dependent. Design dependency means actual delays are not determined until after placement and routing of the user design is complete. Delay values may then be determined by using the ALS Timer utility or performing simulation with post-layout delays.

#### **Critical Nets and Typical Nets**

Propagation delays are expressed only for typical nets, which are used for initial design performance evaluation. Critical net delays can then be applied to the most time-critical paths. Critical nets are determined by net property assignment prior to placement and routing. Up to 6% of the nets in a design may be designated as critical, while 90% of the nets in a design are typical.

#### **Long Tracks**

Some nets in the design use long tracks. Long tracks are special routing resources that span multiple rows, columns, or modules. Long tracks employ three and sometimes four antifuse

connections. This increases capacitance and resistance, resulting in longer net delays for macros connected to long tracks. Typically, up to 6% of nets in a fully utilized device require long tracks. Long tracks contribute approximately 5 ns to 10 ns delay. This additional delay is represented statistically in higher fanout (FO=8) routing delays in the datasheet specifications section.

**Timing Derating**

A best case timing derating factor of 0.45 is used to reflect best case processing. Note that this factor is relative to the "standard speed" timing parameters, and must be multiplied by the

appropriate voltage and temperature derating factors for a given application.

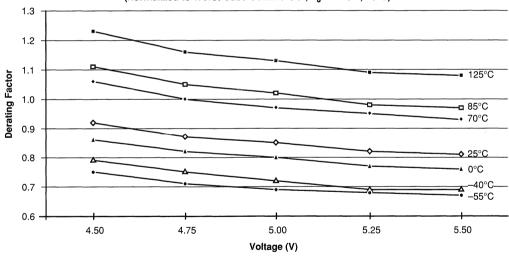

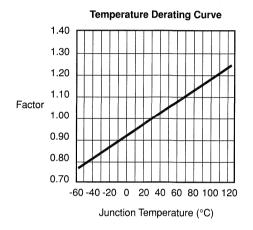

# Timing Derating Factor (Temperature and Voltage)

|                                              | Indu | strial | Military |      |  |

|----------------------------------------------|------|--------|----------|------|--|

|                                              | Min. | Max.   | Min.     | Max. |  |

| (Commercial Minimum/Maximum Specification) x | 0.69 | 1.11   | 0.67     | 1.23 |  |

# Timing Derating Factor for Designs at Typical Temperature (T<sub>J</sub> = 25°C) and Voltage (5.0 V)

(Commercial Maximum Specification) x

0.85

# Temperature and Voltage Derating Factors (normalized to Worst-Case Commercial, $T_J$ = 4.75 V, 70°C)

|      | -55  | -40  | 0    | 25   | 70   | 85   | 125  |

|------|------|------|------|------|------|------|------|

| 4.50 | 0.75 | 0.79 | 0.86 | 0.92 | 1.06 | 1.11 | 1.23 |

| 4.75 | 0.71 | 0.75 | 0.82 | 0.87 | 1.00 | 1.05 | 1.16 |

| 5.00 | 0.69 | 0.72 | 0.80 | 0.85 | 0.97 | 1.02 | 1.13 |

| 5.25 | 0.68 | 0.69 | 0.77 | 0.82 | 0.95 | 0.98 | 1.09 |

| 5.50 | 0.67 | 0.69 | 0.76 | 0.81 | 0.93 | 0.97 | 1.08 |

# Junction Temperature and Voltage Derating Curves (normalized to Worst-Case Commercial, $T_J = 4.75 \text{ V}$ , $70^{\circ}\text{C}$ )

Note:

This derating factor applies to all routing and propagation delays.

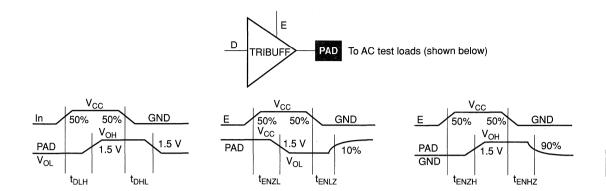

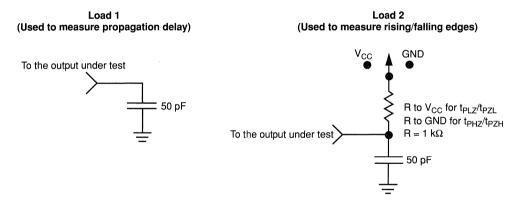

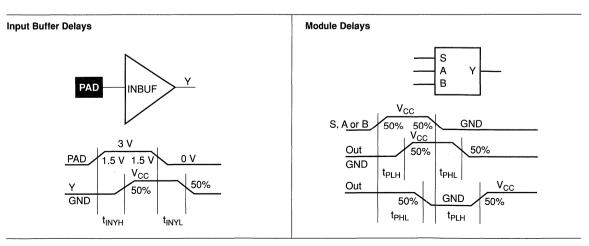

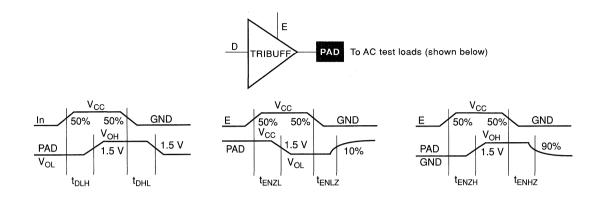

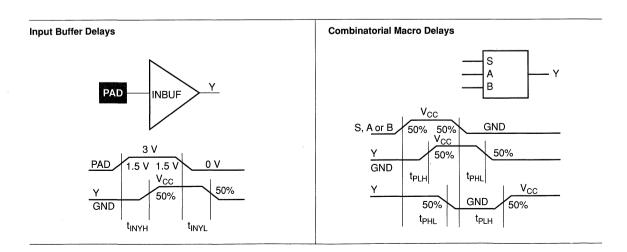

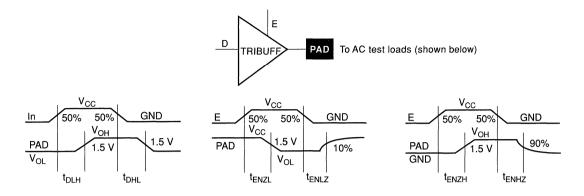

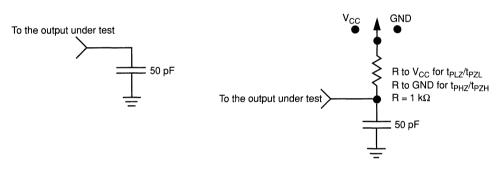

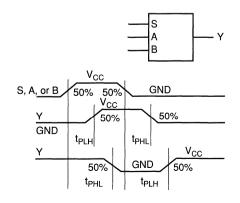

#### **Parameter Measurement**

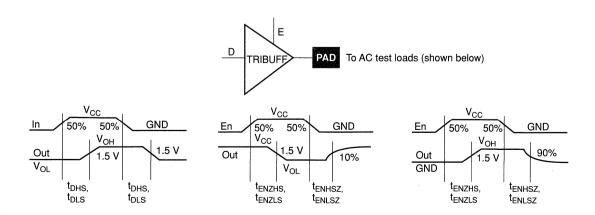

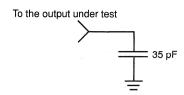

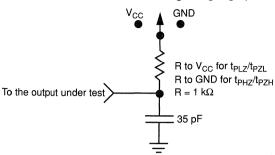

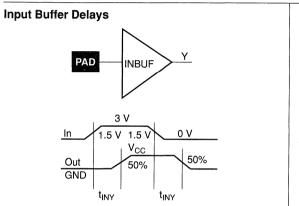

#### **Output Buffer Delays**

**AC Test Loads**

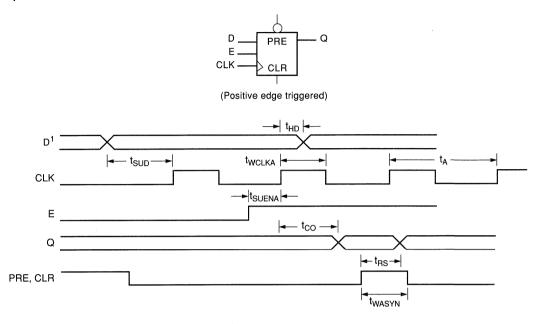

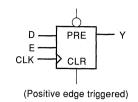

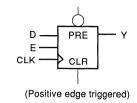

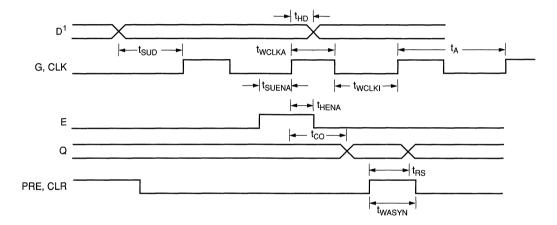

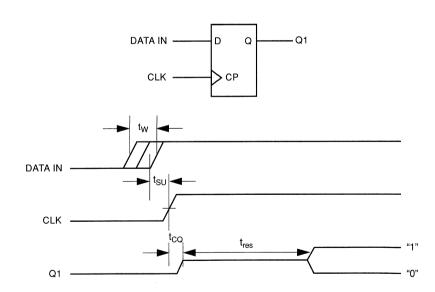

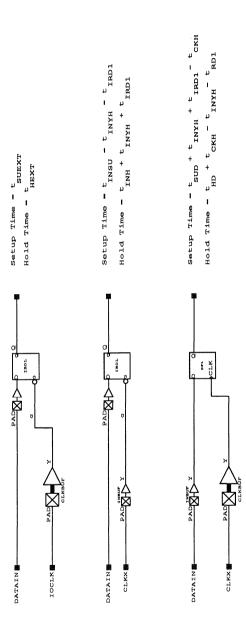

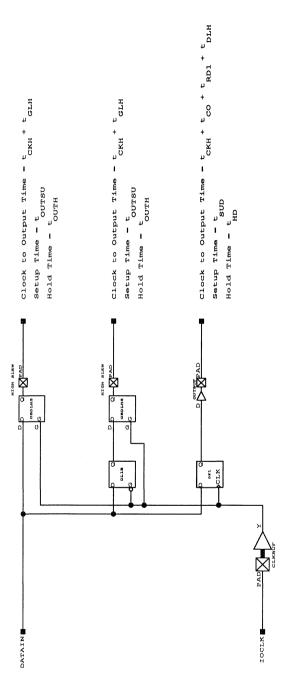

# **Sequential Timing Characteristics**

# Flip-Flops and Latches

#### Note:

1. D represents all data functions involving A, B, and S for multiplexed flip-flops.

**ACT 1 Timing Characteristics**

(Worst-Case Commercial Conditions,  $V_{CC} = 4.75 \text{ V}$ ,  $T_J = 70^{\circ}\text{C}$ )

| Logic Modu         | le Propagation Delays                           | 'Std' | Speed | '-1' Speed |      | '-2' Speed    |      |       |

|--------------------|-------------------------------------------------|-------|-------|------------|------|---------------|------|-------|

| Parameter          | Description                                     | Min.  | Max.  | Min.       | Max. | Min.          | Max. | Units |

| t <sub>PD1</sub>   | Single Module                                   |       | 4.5   |            | 3.8  |               | 3.4  | ns    |

| t <sub>PD2</sub>   | Dual Module Macros                              |       | 10.4  |            | 8.8  |               | 7.8  | ns    |

| $t_{CO}$           | Sequential Clk to Q                             |       | 4.5   |            | 3.8  |               | 3.4  | ns    |

| $t_{GO}$           | Latch G to Q                                    |       | 4.5   |            | 3.8  |               | 3.4  | ns    |

| t <sub>RS</sub>    | Flip-Flop (Latch) Reset to Q                    |       | 4.5   |            | 3.8  |               | 3.4  | ns    |

| Predicted R        | outing Delays <sup>1</sup>                      |       |       |            |      |               |      |       |

| t <sub>RD1</sub>   | FO=1 Routing Delay                              |       | 1.4   |            | 1.2  | Marie Company | 1.1  | ns    |

| t <sub>RD2</sub>   | FO=2 Routing Delay                              |       | 2.2   |            | 1.9  |               | 1.7  | ns    |

| t <sub>RD3</sub>   | FO=3 Routing Delay                              |       | 3.3   |            | 2.8  |               | 2.5  | ns    |

| t <sub>RD4</sub>   | FO=4 Routing Delay                              |       | 4.8   |            | 4.1  |               | 3.6  | ns    |

| t <sub>RD8</sub>   | FO=8 Routing Delay                              |       | 10.2  |            | 8.7  |               | 7.7  | ns    |

| Sequential 1       | Fiming Characteristics <sup>2</sup>             |       |       |            |      |               |      |       |

| t <sub>SUD</sub>   | Flip-Flop (Latch) Data Input<br>Setup           | 8.5   |       | 7.2        |      | 6.4           |      | ns    |

| t <sub>HD</sub>    | Flip-Flop (Latch) Data Input<br>Hold            | 0.0   |       | 0.0        |      | 0.0           |      | ns    |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Enable Setup                  | 8.5   |       | 7.2        |      | 6.4           |      | ns    |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Enable Hold                   | 0.0   |       | 0.0        |      | 0.0           |      | ns    |

| t <sub>WCLKA</sub> | Flip-Flop (Latch) Clock Active<br>Pulse Width   | 10.5  |       | 9.0        |      | 8.0           |      | ns    |

| t <sub>WASYN</sub> | Flip-Flop (Latch) Asynchro-<br>nous Pulse Width | 10.5  |       | 9.0        |      | 8.0           |      | ns    |

| t <sub>A</sub>     | Flip-Flop Clock Input Period                    | 22.3  |       | 18.9       |      | 16.7          |      | ns    |

| f <sub>MAX</sub>   | Flip-Flop (Latch) Clock<br>Frequency (FO = 128) |       | 45    |            | 53   |               | 60   | MHz   |

#### Notes:

<sup>1.</sup> Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

<sup>2.</sup> Setup times assume fanout of 3. Further testing information can be obtained from the ALS Timer utility.

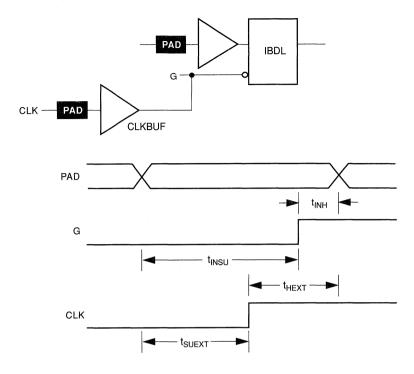

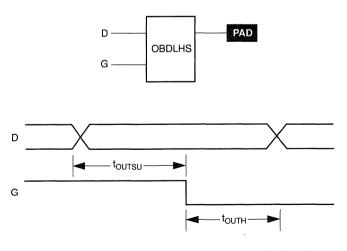

**ACT 1 Timing Characteristics** (continued)

(Worst-Case Commercial Conditions)

| Input Modu        | le Propagation Delays      |                     | 'Std'        | Speed       | '–1' \$                                | Speed      | ' <b>–2</b> ' § | Speed      |       |

|-------------------|----------------------------|---------------------|--------------|-------------|----------------------------------------|------------|-----------------|------------|-------|

| Parameter         | Description                |                     | Min.         | Max.        | Min.                                   | Max.       | Min.            | Max.       | Units |

| t <sub>INYH</sub> | Pad to Y High              |                     |              | 4.7         | ······································ | 4.0        |                 | 3.5        | ns    |

| $t_{INYL}$        | Pad to Y Low               |                     |              | 4.7         |                                        | 4.0        |                 | 3.5        | ns    |

| Input Modu        | le Predicted Routing Delay | s <sup>1</sup>      |              |             |                                        |            |                 |            |       |

| t <sub>IRD1</sub> | FO=1 Routing Delay         |                     |              | 1.4         | <u> </u>                               | 1.2        |                 | 1.1        | ns    |

| t <sub>IRD2</sub> | FO=2 Routing Delay         |                     |              | 2.2         |                                        | 1.9        |                 | 1.7        | ns    |

| $t_{\text{IRD3}}$ | FO=3 Routing Delay         |                     |              | 3.3         |                                        | 2.8        |                 | 2.5        | ns    |

| $t_{IRD4}$        | FO=4 Routing Delay         |                     |              | 4.8         |                                        | 4.1        |                 | 3.6        | ns    |

| $t_{IRD8}$        | FO=8 Routing Delay         |                     |              | 10.2        |                                        | 8.7        |                 | 7.7        | ns    |

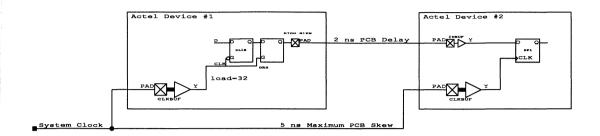

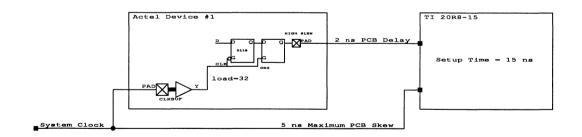

| Global Clo        | ck Network                 |                     |              |             |                                        |            |                 |            |       |

| t <sub>CKH</sub>  | Input Low to High          | FO = 16<br>FO = 128 |              | 7.5<br>8.6  |                                        | 6.4<br>7.3 |                 | 5.6<br>6.4 | ns    |

| t <sub>CKL</sub>  | Input High to Low          | FO = 16<br>FO = 128 |              | 9.9<br>10.8 |                                        | 8.4<br>9.2 |                 | 7.4<br>8.1 | ns    |

| t <sub>PWH</sub>  | Minimum Pulse Width High   | FO = 16<br>FO = 128 | 10.0<br>10.5 |             | 8.5<br>9.0                             |            | 7.5<br>8.0      |            | ns    |

| t <sub>PWL</sub>  | Minimum Pulse Width Low    | FO = 16<br>FO = 128 | 10.0<br>10.5 |             | 8.5<br>9.0                             |            | 7.5<br>8.0      |            | ns    |

| t <sub>CKSW</sub> | Maximum Skew               | FO = 16<br>FO = 128 |              | 1.8<br>2.8  |                                        | 1.5<br>2.4 |                 | 1.3<br>2.1 | ns    |

| t <sub>P</sub>    | Minimum Period             | FO = 16<br>FO = 128 | 20.9<br>22.3 |             | 17.6<br>18.9                           |            | 15.4<br>16.7    |            | ns    |

| $f_{MAX}$         | Maximum Frequency          | FO = 16<br>FO = 128 |              | 48<br>45    |                                        | 57<br>53   |                 | 65<br>60   | MHz   |

#### Note:

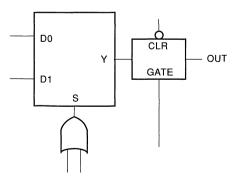

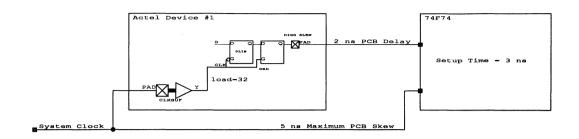

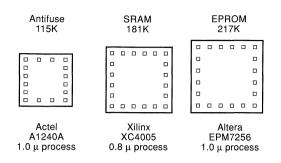

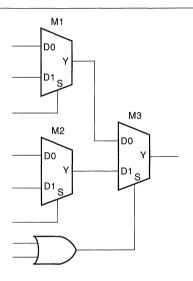

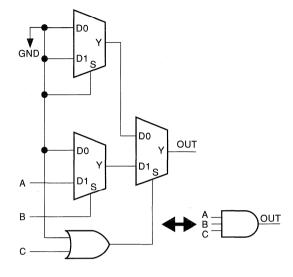

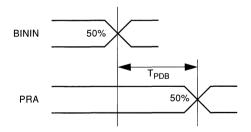

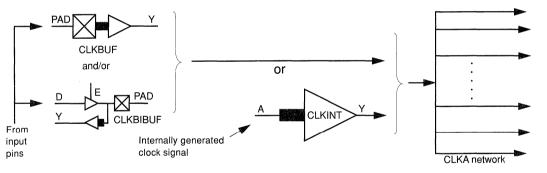

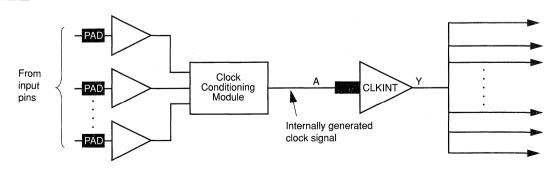

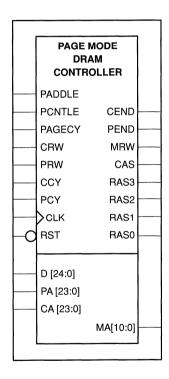

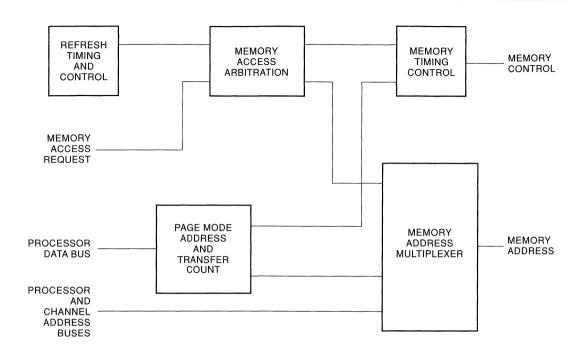

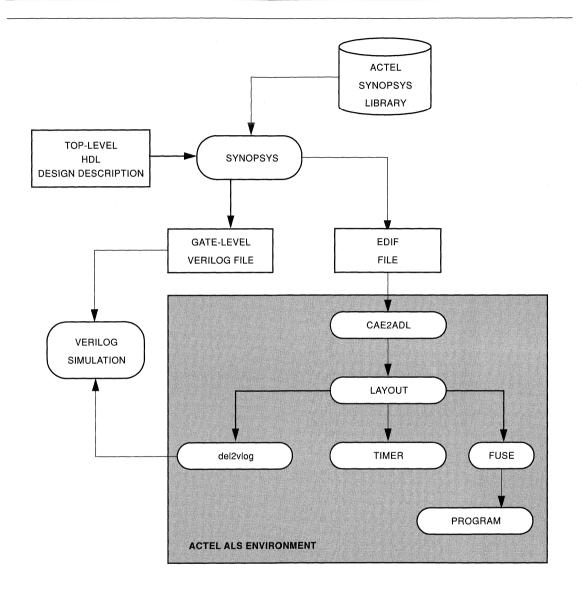

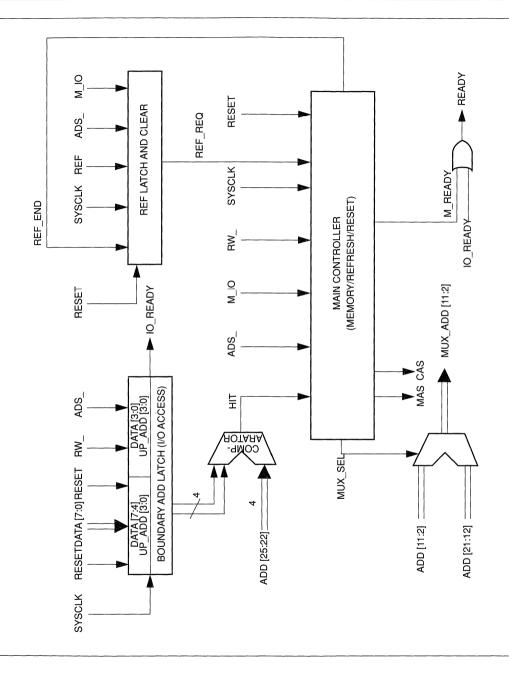

<sup>1.</sup> These parameters should be used for estimating device performance. Optimization techniques may further reduce delays by 0 to 4 ns. Routing delays are for typical designs across worst-case operating conditions. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.